- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C974 (Advanced Micro Devices, Inc.) PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C974 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| 中文描述: | PCnetTM -的SCSI結(jié)合以太網(wǎng)和SCSI控制器PCI系統(tǒng) |

| 文件頁(yè)數(shù): | 69/153頁(yè) |

| 文件大小: | 838K |

| 代理商: | AM79C974 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)當(dāng)前第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)

P R E L I M I N A R Y

AMD

69

Am79C974

Transmit Operation

The transmit operation and features of the Am79C974

controller are controlled by programmable options. The

Am79C974 controller offers a136-byte Transmit FIFO to

provide frame buffering for increased system latency,

automatic retransmission with no FIFO reload, and

automatic transmit padding.

Transmit Function Programming

Automatic transmit features such as retry on collision,

FCS generation/transmission, and pad field insertion

can all be programmed to provide flexibility in the

(re-)transmission of messages.

Disable retry on collision (DRTY) is controlled by the

DRTY bit of the Mode register (CSR15) in the initiali-

zation block.

Automatic pad field insertion is controlled by the

APAD_XMT bit in CSR4. If APAD_XMT is set, auto-

matic pad field insertion is enabled, the DXMTFCS fea-

ture is over-ridden, and the 4-byte FCS will be added to

the transmitted frame unconditionally. If APAD_XMT is

clear, no pad field insertion will take place and runt

packet transmission is possible.

The disable FCS generation/transmission feature can

be programmed dynamically on a frame by frame basis.

See the ADD_FCS description of TMD1.

Transmit FIFO Watermark (XMTFW) in CSR80 sets the

point at which the BMU requests more data from the

transmit buffers for the FIFO. A minimum of XMTFW

empty spaces must be available in the transmit FIFO be-

fore the BMU will request the system bus in order to

transfer transmit packet data into the transmit FIFO.

Transmit Start Point (XMTSP) in CSR80 sets the point

when the transmitter actually attempts to transmit a

frame onto the media. A minimum of XMTSP bytes must

be written to the transmit FIFO for the current frame be-

fore transmission of the current frame will begin. (When

automatically padded packets are being sent, it is con-

ceivable that the XMTSP is not reached when all of the

data has been transferred to the FIFO. In this case, the

transmission will begin when all of the packet data has

been placed into the transmit FIFO.)

When the entire frame is in the FIFO, attempts at trans-

mission of preamble will commence regardless of the

value in XMTSP. The default value of XMTSP is 10b,

meaning there has to be 64 bytes in the Transmit FIFO

to start a transmission.

Automatic Pad Generation

Transmit frames can be automatically padded to extend

them to 64 data bytes (excluding preamble). This allows

the minimum frame size of 64 bytes (512 bits) for

802.3/Ethernet to be guaranteed with no software inter-

vention from the host/controlling process.

Setting the APAD_XMT bit in CSR4 enables the auto-

matic padding feature. The pad is placed between the

LLC data field and FCS field in the 802.3 frame.FCS is

always added if the frame is padded, regardless of the

state of DXMTFCS. The transmit frame will be padded

by bytes with the value of 00h. The default value of

APAD_XMT is 0; this will disable auto pad generation af-

ter H_RESET.

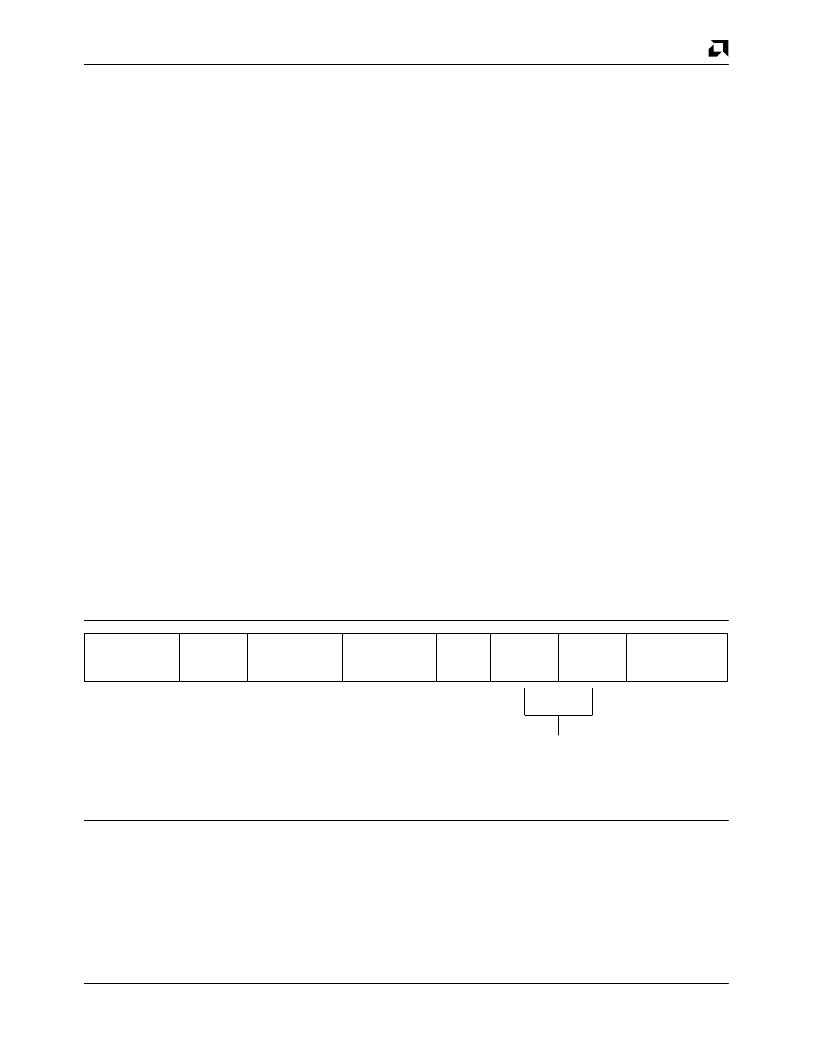

Preamble

1010....1010

Sync

10101011

Destination

Address

Source

Address

Length

LLC

Data

Pad

FCS

4

Bytes

46 — 1500

Bytes

2

Bytes

6

Bytes

6

Bytes

8

Bits

56

Bits

18681A-26

Figure 22

.

ISO 8802-3 (IEEE/ANSI 802.3) Data Frame

It is the responsibility of upper layer software to correctly

define the actual length field contained in the message

to correspond to the total number of LLC Data bytes en-

capsulated in the packet (length field as defined in the

ISO 8802-3 (IEEE/ANSI 802.3) standard). The length

value contained in the message is not used by the

Am79C974 controller to compute the actual number of

pad bytes to be inserted. The Am79C974 controller will

append pad bytes dependent on the actual number of

bits transmitted onto the network. Once the last data

byte of the frame has completed, prior to appending the

FCS, the Am79C974 controller will check to ensure that

544 bits have been transmitted. If not, pad bytes are

added to extend the frame size to this value, and the

FCS is then added.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C974KCW | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C975KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C974KC | 制造商:Advanced Micro Devices 功能描述: |

| AM79C974KC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C974KCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。