- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C974 (Advanced Micro Devices, Inc.) PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems PDF資料下載

參數(shù)資料

| 型號: | AM79C974 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| 中文描述: | PCnetTM -的SCSI結(jié)合以太網(wǎng)和SCSI控制器PCI系統(tǒng) |

| 文件頁數(shù): | 53/153頁 |

| 文件大小: | 838K |

| 代理商: | AM79C974 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當(dāng)前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

P R E L I M I N A R Y

AMD

53

Am79C974

The oscillator requires an external 0.01% timing refer-

ence. The accuracy requirements, if an external crystal

is used are tighter because allowance for the on-board

parasitics must be made to deliver a final accuracy of

0.01%.

Transmission is enabled by the controller. As long as the

ITXEN request remains active, the serial output of the

controller will be Manchester encoded and appear at

DO

±

. When the internal request is dropped by the con-

troller, the differential transmit outputs go to one of two

idle states, dependent on TSEL in the Mode Register

(CSR15, bit 9):

TSEL LOW:

The idle state of DO

±

yields “ZERO”

differential to operate transformer-

coupled loads.

TSEL HIGH: In this idle state, DO+ is positive with

respect to DO– (logical HIGH).

Receiver Path

The principal functions of the Receiver are to signal the

Am79C974 controller that there is information on the re-

ceive pair, and separate the incoming Manchester en-

coded data stream into clock and NRZ data.

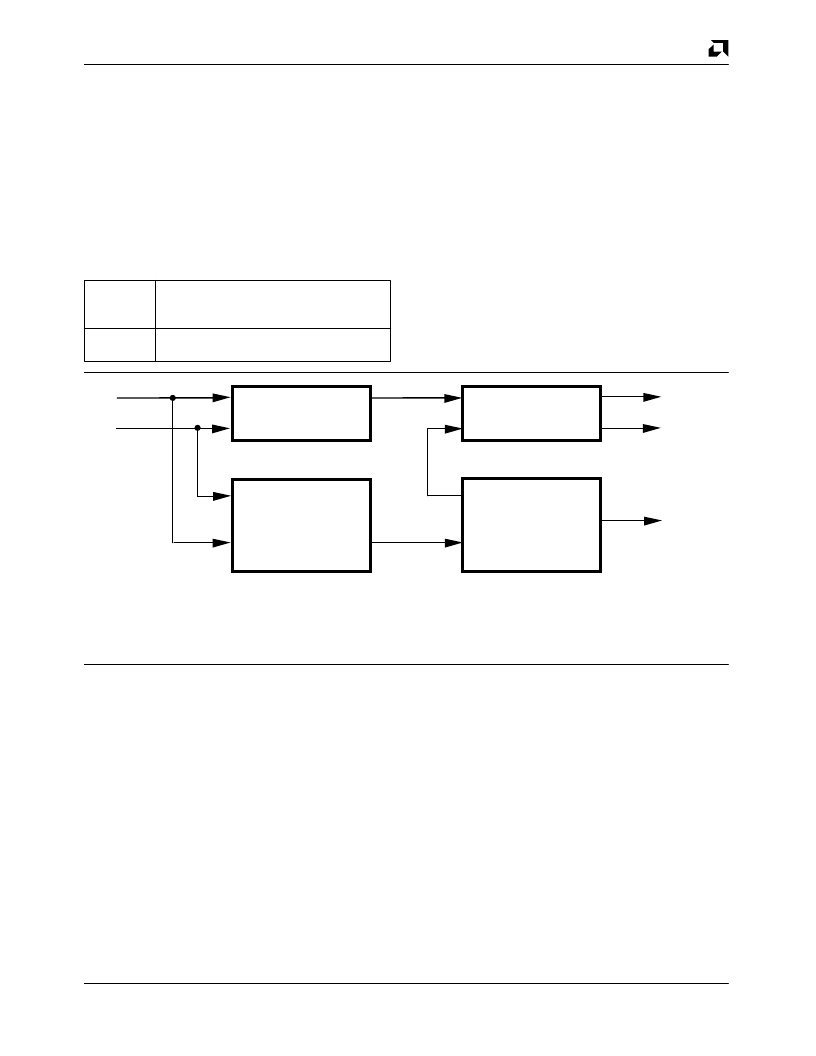

The Receiver section (see Receiver Block Diagram)

consists of two parallel paths. The receive data path is a

ZERO threshold, wide bandwidth line receiver. The car-

rier path is an offset threshold bandpass detecting line

receiver. Both receivers share common bias networks

to allow operation over a wide input common

moderange.

18681A-23

Noise

Reject

Filter

Data

Receiver

Carrier

Detect

Circuit

Manchester

Decoder

IRXDAT*

ISRDCLK*

IRXCRS*

DI

±

*Internal signal

Figure 19

.

Receiver Block Diagram

Input Signal Conditioning

Transient noise pulses at the input data stream are re-

jected by the Noise Rejection Filter. Pulse width rejec-

tion is proportional to transmit data rate, (which is fixed

at 10 MHz for Ethernet but could be different for proprie-

tary networks). DC inputs more negative than minus

100 mV are also surpressed.

The Carrier Detection circuitry detects the presence of

an incoming data frame by discerning and rejecting

noise from expected Manchester data, and controls the

stop and start of the phase-lock loop during clock acqui-

sition. Clock acquisition requires a valid Manchester bit

pattern of 1010b to lock onto the incoming message.

When input amplitude and pulse width conditions are

met at DI

±

, the internal enable signal from the MENDEC

to controller (IRXCRS) is asserted and a clock acquisi-

tion cycle is initiated.

Clock Acquisition

When there is no activity at DI

±

(receiver is idle), the re-

ceive oscillator is phase locked to internal transmit

clock. The first negative clock transition (bit cell center of

first valid Manchester “0”) after IRXCRS is asserted in-

terrupts the receive oscillator. The oscillator is then re-

started at the second Manchester “0” (bit time 4) and is

phase locked to it. As a result, the MENDEC acquires

the clock from the incoming Manchester bit pattern in

4bit times with a 1010b Manchester bit pattern.

The internal serial receive data clock, ISRDCLK and the

internal received data, IRXDAT, are enabled 1/4 bit time

after clock acquisition in bit cell 5. IRXDAT is at a HIGH

state when the receiver is idle (no ISRDCLK). IRXDAT

however, is undefined when clock is acquired and may

remain HIGH or change to LOW state whenever

ISRDCLK is enabled. At 1/4 bit time through bit cell 5,

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C974KCW | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C975KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C974KC | 制造商:Advanced Micro Devices 功能描述: |

| AM79C974KC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C974KCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。