- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366550 > AM79C960KC (ADVANCED MICRO DEVICES INC) PCnetTM-ISA Single-Chip Ethernet Controller PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C960KC |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | PCnetTM-ISA Single-Chip Ethernet Controller |

| 中文描述: | 2 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP120 |

| 封裝: | CARRIER RING, PLASTIC, QFP-120 |

| 文件頁(yè)數(shù): | 57/127頁(yè) |

| 文件大小: | 814K |

| 代理商: | AM79C960KC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)當(dāng)前第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)

P R E L I M I N A R Y

AMD

1-399

Am79C960

Receive FCS Checking

Reception and checking of the received FCS is per-

formed automatically by the PCnet-ISA controller. Note

that if the Automatic Pad Stripping feature is enabled,

the received FCS will be verified against the value com-

puted for the incoming bit stream including pad

characters, but it will not be passed to the host. If a FCS

error is detected, this will be reported by the CRC bit in

RMD1.

Receive Exception Conditions

Exception conditions for frame reception fall into two

distinct categories; those which are the result of normal

network operation, and those which occur due to abnor-

mal network and/or host related events.

Normal events which may occur and which are handled

autonomously by the PCnet-ISA controller are basically

collisions within the slot time and automatic runt packet

rejection. The PCnet-ISA controller will ensure that colli-

sions which occur within 512 bit times from the start of

reception (excluding preamble) will be automatically de-

leted from the receive FIFO with no host intervention.

The receive FIFO will delete any frame which is com-

posed of fewer than 64 bytes provided that the Runt

Packet Accept (RPA bit in CSR124) feature has not

been enabled. This criteria will be met regardless of

whether the receive frame was the first (or only) frame in

the FIFO or if the receive frame was queued behind a

previously received message.

Abnormal network conditions include:

I

FCS errors

I

Late collision

These should not occur on a correctly configured 802.3

network and will be reported if they do.

Host related receive exception conditions include MISS,

BUFF, and OFLO. These are described in the Receive

Descriptor section.

Loopback Operation

During loopback, the FCS logic can be allocated to the

receiver by setting the DXMTFCS bit in CSR15.

If DXMTFCS=0, the MAC Engine will calculate and ap-

pend the FCS to the transmitted message. In this

loopback configuration, the receive circuitry cannot de-

tect FCS errors if they occur.

If DXMTFCS=1, the last four bytes of the transmit mes-

sage must contain the (software generated) FCS

computed for the transmit data preceding it. The MAC

Engine will transmit the data without addition of an FCS

field, and the FCS will be calculated and verified at the

receiver.

The loopback facilities of the MAC Engine allow full op-

eration to be verified without disturbance to the network.

Loopback operation is also affected by the state of the

Loopback Control bits (LOOP, MENDECL, and INTL) in

CSR15. This affects whether the internal MENDEC is

considered part of the internal or external loopback

path.

When in the loopback mode(s), the multicast address

detection feature of the MAC Engine, programmed by

the contents of the Logical Address Filter (LADRF [63:0]

in CSR 8-11) can only be tested when DXMTFCS= 1, al-

locating the FCS generator to the receiver. All other

features operate identically in loopback as in normal op-

eration, such as automatic transmit padding and receive

pad stripping.

When performing an internal loopback, no frame will be

transmitted to the network. However, when the

PCnet-ISA controller is configured for internal loopback

the receiver will not be able to detect network traffic. AUI

external loopback tests will transmit frames onto the net-

work, and the PCnet-ISA controller will receive network

traffic while configured for external loopback. 10BASE-

T external loopback should never be used in a live

network. 10BASE-T external loopback provides a

means of looping Transmit data to the receive input

without asserting a collision. This mode allows a board

test to verify both the transmit and receive paths to the

10BASE-T connector. Unless the Runt Packet Accept

feature is enabled, all loopback frames must contain at

least 64 bytes of data.

LEDs

The PCnet-ISA controller’s LED control logic allows pro-

gramming of the status signals, which are displayed on

3 LED outputs. One LED (

LED0

) is dedicated to display-

ing 10BASE-T Link Status. The status signals available

are Collision, Jabber, Receive, Receive Polarity (active

when receive polarity is okay), and Transmit. If more

than one status signal is enabled, they are ORed to-

gether. An optional pulse stretcher is available for each

programmable output. This allows emulation of the

TPEX (Am79C98) and TPEX+ (Am79C100) LED

outputs.

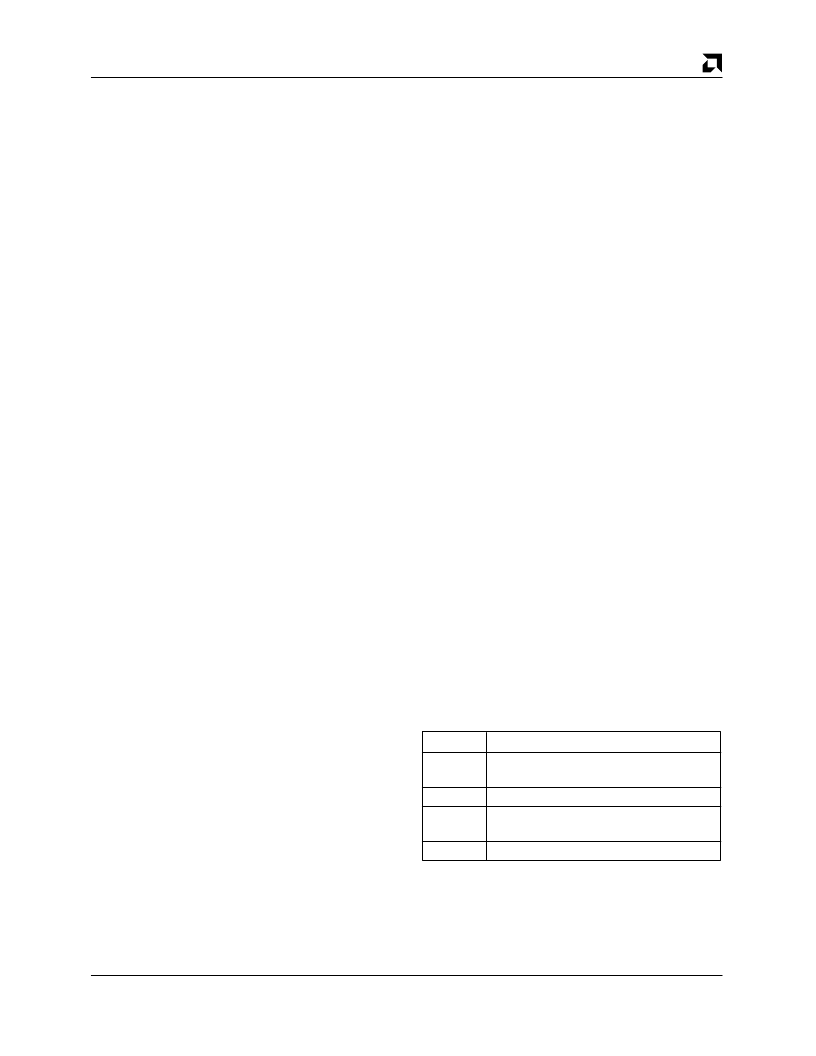

Signal

Behavior

LNKST

Active during Link OK

Not active during Link Down

RCV

Active while receiving data

RVPOL

Active during receive polarity is OK

Not active during reverse receive polarity

XMT

Active while transmitting data

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C960KCW | PCnetTM-ISA Single-Chip Ethernet Controller |

| AM79C961AKCW | PCnet ⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

| AM79C961AKC | PCnet ⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

| AM79C961A | PCnet ⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

| AM79C961AKIW | PCnet⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C960KC/W | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:LAN Node Controller |

| AM79C960KCW | 制造商:AMD 制造商全稱(chēng):Advanced Micro Devices 功能描述:PCnetTM-ISA Single-Chip Ethernet Controller |

| AM79C961 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Am79C961 - PCnet-ISA+ Jumperless Single-Chip Ethernet Controller for ISA |

| AM79C961/AM79C961A | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Using the Am79C961/Am79C961A (PCnet-ISA+/PCnet-ISA II) Survival Guide? 134KB (PDF) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。