- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373857 > AD14160LKB-4 (ANALOG DEVICES INC) Quad-SHARC DSP Multiprocessor Family PDF資料下載

參數(shù)資料

| 型號(hào): | AD14160LKB-4 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | Quad-SHARC DSP Multiprocessor Family |

| 中文描述: | 48-BIT, 40 MHz, OTHER DSP, CBGA452 |

| 封裝: | CERAMIC, BGA-452 |

| 文件頁(yè)數(shù): | 32/52頁(yè) |

| 文件大?。?/td> | 1193K |

| 代理商: | AD14160LKB-4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

AD14160/AD14160L

–32–

REV. A

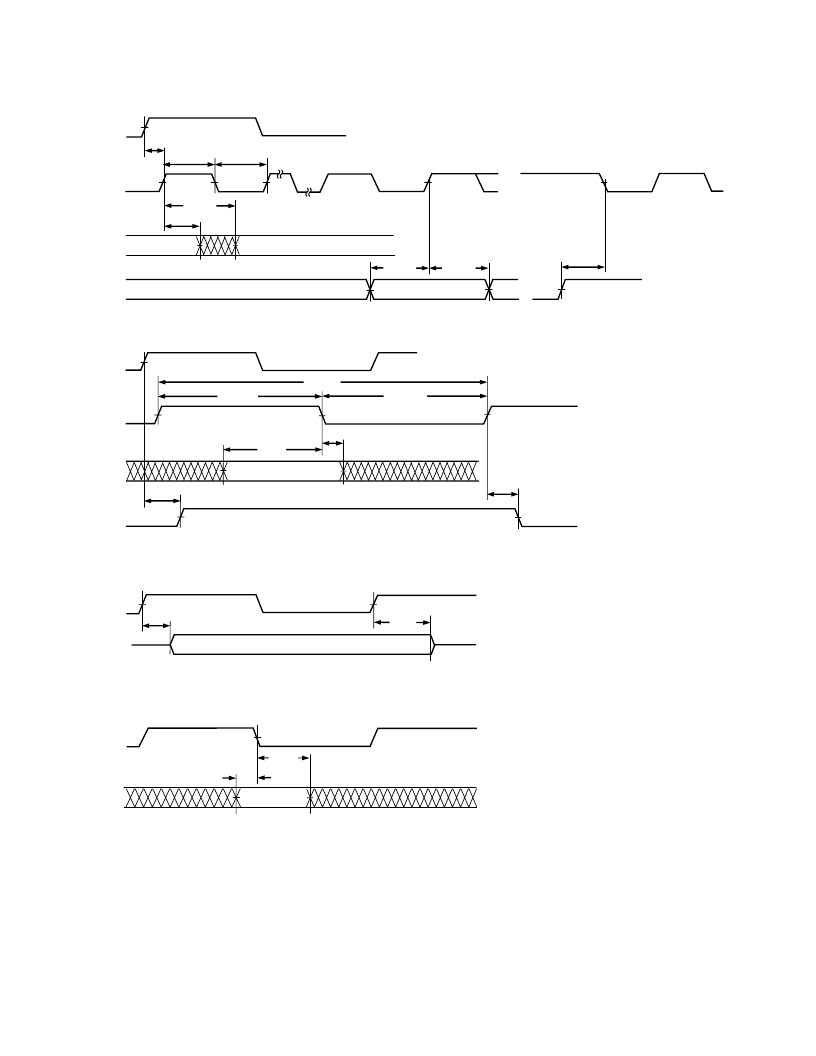

CLKIN

LCLK

LDAT(3:0)

LACK

LCLK 1x

OR

LCLK 2x

CLKIN

LDAT(3:0)

LACK (IN)

LCLK 1x

OR

LCLK 2x

LDAT(3:0)

LACK (OUT)

THE

t

SLACH

REQUIREMENT APPLIES TO THE RISING EDGE OF LCLK ONLY FOR THE FIRST NIBBLE TRANSMITTED.

CLKIN

TRANSMIT

t

DLDCH

t

HLDCH

t

DLCLK

t

LCLKTWH

t

LCLKTWL

t

SLACH

t

HLACH

t

DLACLK

t

SLDCL

t

HLDCL

t

LCLKRWH

t

DLAHC

t

DLALC

LINK PORT ENABLE OR THREE-STATE TAKES EFFECT 2 CYCLES AFTER A WRITE TO A LINK PORT CONTROL REGISTER.

t

ENDLK

t

TDLK

RECEIVE

LINK PORT ENABLE/THREE-STATE DELAY FROM INSTRUCTION

t

LCLKRWL

t

LCLKIW

CLKIN

t

SLCK

t

HLCK

LINK PORT INTERRUPT SETUP TIME

LCLK

LACK

LAST NIBBLE

TRANSMITTED

FIRST NIBBLE

TRANSMITTED

LCLK INACTIVE

(HIGH)

OUT

IN

LACK GOES LOW ONLY AFFTER THE SECOND NIBBLE IS RECEIVED.

Figure 22. Link Ports

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1555-AD1556 | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555AP | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555APRL | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555BP | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555BPRL | 24-Bit ADC WITH LOW NOISE PGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD142 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | BJT | PNP | 80V V(BR)CEO | 10A I(C) | TO-3 |

| AD143 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | BJT | PNP | 40V V(BR)CEO | 10A I(C) | TO-3 |

| AD-1432-ACD10FT-LPG-HOSE | 制造商:TE Connectivity 功能描述: |

| AD-1434-ACD30FT-LPG-HOSE | 制造商:TE Connectivity 功能描述: |

| AD-1446-TERMNTG-FIXTUR | 制造商:TE Connectivity 功能描述:AD-1446-TERMNTG-FIXTURE |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。