- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373857 > AD14160LKB-4 (ANALOG DEVICES INC) Quad-SHARC DSP Multiprocessor Family PDF資料下載

參數(shù)資料

| 型號: | AD14160LKB-4 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | Quad-SHARC DSP Multiprocessor Family |

| 中文描述: | 48-BIT, 40 MHz, OTHER DSP, CBGA452 |

| 封裝: | CERAMIC, BGA-452 |

| 文件頁數(shù): | 22/52頁 |

| 文件大?。?/td> | 1193K |

| 代理商: | AD14160LKB-4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

AD14160/AD14160L

–22–

REV. A

40 MHz–5 V

Min

40 MHz–3.3 V

Min

Parameter

Max

Max

Units

Timing Requirements:

t

SADRI

t

HADRI

t

SRWLI

t

HRWLI

t

RWHPI

t

SDATWH

t

HDATWH

Address,

SW

Setup Before CLKIN

Address,

SW

Hold Before CLKIN

RD

/

WR

Low Setup Before CLKIN

1

RD

/

WR

Low Hold After CLKIN

RD

/

WR

Pulse High

Data Setup Before

WR

High

Data Hold After

WR

High

15.5 + DT/2

15.5 + DT/2

ns

ns

ns

ns

ns

ns

ns

5 + DT/2

5 + DT/2

10 + 5DT/16

–4 – 5DT/16

3

6

1.5

10 + 5DT/16

–4 – 5DT/16

3

6

1.5

7.5 + 7DT/16

7.5 + 7DT/16

Switching Characteristics:

t

SDDATO

t

DATTR

t

DACKAD

t

ACKTR

Data Delay After CLKIN

Data Disable After CLKIN

2

ACK Delay After Address,

SW

3

ACK Disable After CLKIN

3

20 + 5DT/16

8 – DT/8

10

7 – DT/8

20 + 5DT/16

8 – DT/8

10

7 – DT/8

ns

ns

ns

ns

0 – DT/8

0 – DT/8

–1 – DT/8

–1 – DT/8

NOTES

1

t

SRWLI

(min) = 10 + 5DT/16 when Multiprocessor Memory Space Wait State (MMSWS bit in WAIT register) is disabled; when MMSWS is enabled,

t

(min) = 4.5 + DT/8.

2

See System Hold Time Calculation under Test Conditions for calculation of hold times given capacitive and dc loads.

3

t

is true only if the address and

SW

inputs have setup times (before CLKIN) greater than 10.5 + DT/8 and less than 19 + 3DT/4. If the address and

SW

inputs have

setup times greater than 19 + 3DT/4, then ACK is valid 15 + DT/4 (max) after CLKIN. A slave that sees an address with an M field match will respond with ACK

regardless of the state of MMSWS or strobes. A slave will three-state ACK every cycle with t

ACKTR

.

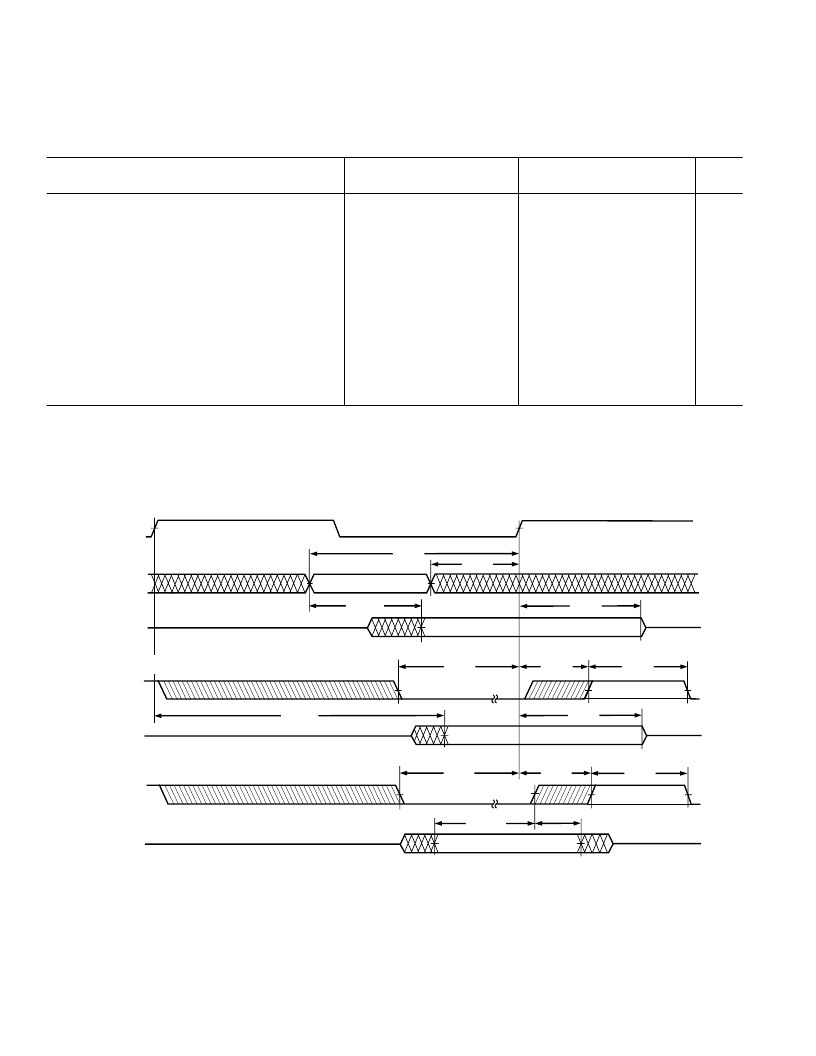

CLKIN

ADDRESS

SW

ACK

RD

DATA

(OUT)

WR

WRITE ACCESS

t

SADRI

t

HADRI

t

DACKAD

t

ACKTR

t

RWHPI

t

HRWLI

t

SRWLI

t

SDDATO

t

DATTR

t

SRWLI

t

HRWLI

t

RWHPI

t

HDATWH

t

SDATWH

DATA

(IN)

READ ACCESS

Figure 17. Synchronous Read/Write—Bus Slave

Synchronous Read/Write—Bus Slave

Use these specifications for bus master accesses of a slave’s IOP

registers or internal memory (in multiprocessor memory space).

The bus master must meet these (bus slave) timing requirements.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1555-AD1556 | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555AP | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555APRL | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555BP | 24-Bit ADC WITH LOW NOISE PGA |

| AD1555BPRL | 24-Bit ADC WITH LOW NOISE PGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD142 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | BJT | PNP | 80V V(BR)CEO | 10A I(C) | TO-3 |

| AD143 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRANSISTOR | BJT | PNP | 40V V(BR)CEO | 10A I(C) | TO-3 |

| AD-1432-ACD10FT-LPG-HOSE | 制造商:TE Connectivity 功能描述: |

| AD-1434-ACD30FT-LPG-HOSE | 制造商:TE Connectivity 功能描述: |

| AD-1446-TERMNTG-FIXTUR | 制造商:TE Connectivity 功能描述:AD-1446-TERMNTG-FIXTURE |

發(fā)布緊急采購,3分鐘左右您將得到回復。