- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67322 > 5962-0924001VXC (TEXAS INSTRUMENTS INC) 1-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | 5962-0924001VXC |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 12-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP100 |

| 封裝: | HERMETIC SEALED, CERAMIC, QFP-100 |

| 文件頁數(shù): | 13/46頁 |

| 文件大小: | 1109K |

| 代理商: | 5962-0924001VXC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

SLAS669B

– SEPTEMBER 2010 – REVISED MAY 2011

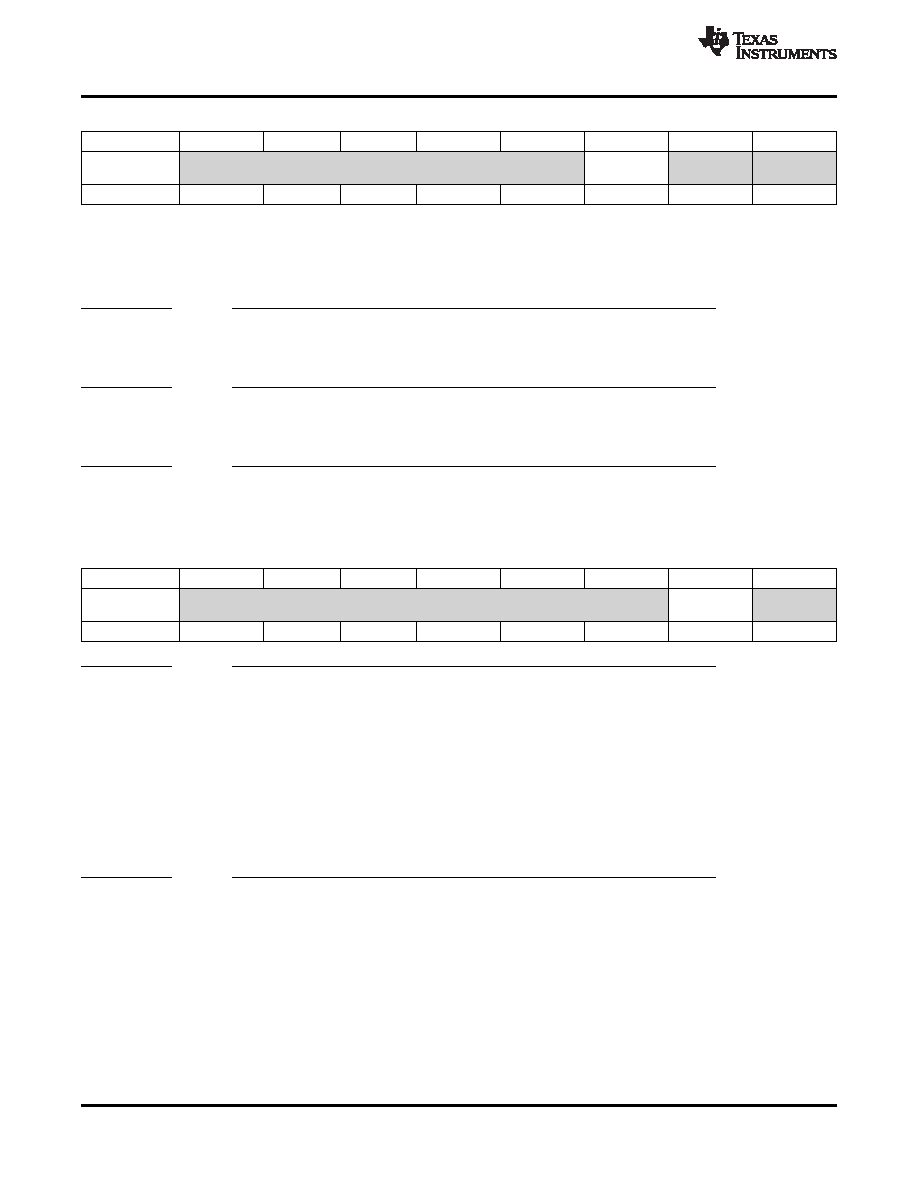

Table 8. Serial Register 0x02 (Read or Write)

Address (hex)

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

Single or

0x02

Coarse Clock Phase Adjustment bits

<4:0>

0

Clock Divider

Dual Bus

Defaults

0

BIT

<0>

Single or Dual Bus Output Selection

0

dual bus output (A and B)

1

single bus output (A)

BIT

<1>

Output Clock Divider

0

CLKOUT equals CLKIN divide by 4 (not available in single bus mode)

1

CLKOUT equals CLKIN divide by 2

BIT

<2>

RESERVED

0

set to 0 if writing this register

1

do not set to 1

BIT

<7:3>

Input Clock Coarse Phase Adjustment

Use as a coarse adjustment of input clock phase. The 5-bit adjustment

provides a step size of ~2.4ps across a range from code 00000 = 0 ps

to code 11111 = 73ps.

Table 9. Serial Register 0x03 (Read or Write)

Address (hex)

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

Analog Offset

0x03

Fine Clock Phase Adjustment bits

<5:0>

0

bit

<8>

Defaults

0

factory set

BIT

<0>

Analog Offset control (most significant bit of 9-bit word)

All 9-bits in this adjustment in address 0x03 and 0x04 set to 0 0000

0000 = -30mV (TBD)

All 9-bits in this adjustment in address 0x03 and 0x04 set to 1 1111

1111 = +30mV (TBD)

Step adjustment resolution is 120

V (or 1/4 LSB). Adjustments can be

used for calibration of analog signal path offset (for instance offset

error induced outside of the ADC) or to match multiple ADC offsets.

The default setting for this register is factory set to provide ~0mV of

ADC offset in the output codes and is unique for each device.

BIT

<1>

RESERVED

0

set to 0 if writing this register

1

do not set to 1

BIT

<7:2>

Fine Clock Phase Adjustment

Use as a fine adjustment of the input clock phase. The 6-bit

adjustment provides a step resolution of ~116fs across a range from

code 000000 = 0ps to code 111111 = 7.4ps. Can be used in conjuction

with Coarse Clock Phase Adjustment in address 0x02.

20

Copyright

2010–2011, Texas Instruments Incorporated

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-3870702MGX | SWITCHED CAPACITOR CONVERTER, MBCY8 |

| 5962-3870702MPX | SWITCHED CAPACITOR CONVERTER, CDIP8 |

| 5962-8512701XC | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 |

| 5962-85127023A | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CQCC28 |

| 5962-8512702XA | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-1022101VSC | 制造商:Texas Instruments 功能描述:HIGH TEMP BUCK CONVERTER - Trays |

| 5962-1123701VXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 16MB Radiation- Hardened 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 5962-1124201VFA | 功能描述:LVDS 接口集成電路 2x2 Crosspoint Sw RoHS:否 制造商:Texas Instruments 激勵(lì)器數(shù)量:4 接收機(jī)數(shù)量:4 數(shù)據(jù)速率:155.5 Mbps 工作電源電壓:5 V 最大功率耗散:1025 mW 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-16 Narrow 封裝:Reel |

| 596-2114-013 | 制造商:Johnson Components 功能描述:WASHER - Bulk |

| 5962-1222401QHA | 功能描述:低壓差控制器 - LDO Lo-NOISE FAST-TRANS 1.5A LDO VTG Reg RoHS:否 制造商:Micrel 最大輸入電壓:5.5 V 輸出電壓:Adjustable 輸出電流:10 mA 負(fù)載調(diào)節(jié): 輸出類型:Adjustable, Fixed 輸出端數(shù)量:1 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOT-23-6 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。