- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358627 > 33742S (Motorola, Inc.) System Basis Chip (SBC) with Enhanced High-Speed CAN Transceiver PDF資料下載

參數(shù)資料

| 型號: | 33742S |

| 廠商: | Motorola, Inc. |

| 元件分類: | CAN |

| 英文描述: | System Basis Chip (SBC) with Enhanced High-Speed CAN Transceiver |

| 中文描述: | 系統(tǒng)基礎(chǔ)芯片的增強型(SBC)的高速CAN收發(fā)器 |

| 文件頁數(shù): | 38/52頁 |

| 文件大小: | 1087K |

| 代理商: | 33742S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當(dāng)前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

33742

38

MOTOROLA ANALOG INTEGRATED CIRCUIT DEVICE DATA

SPI INTERFACE AND REGISTER DESCRIPTION

Data Format Description

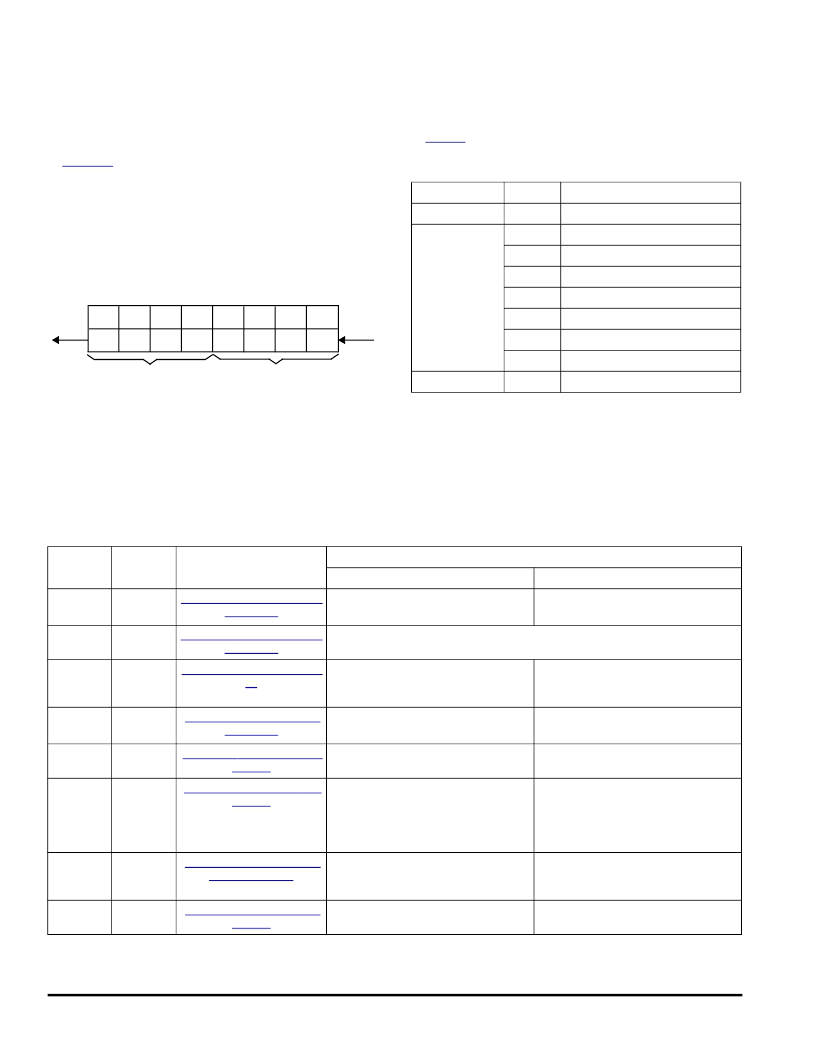

Figure 24

illustrates a register, an 8-bit SPI. The first three

bits are used to identify the internal 33742 register address.

Bit 4 is a read/write bit. The last four bits are data sent from the

MCU to the 33742 or read back from the 33742 to the MCU.

The state of the MISO has no significance during the write

operation. However, during the read operation the final four bits

of MISO have meaning; namely, they contain the content of the

accessed register.

Figure 24. Data Format Description

Table 8

lists the possible reset conditions.

Table 8. Possible Reset Conditions

Register Descriptions

The following tables in this section describe the SPI register

list and register bit meaning. Register reset value is also

described, along with the reset condition. Reset condition is the

condition causing the bit to be set at the reset value.

Bit 7

Bit 5

Bit 3

Bit 4

Bit 2

Bit 6

Bit 1

Bit 0

A2

A0

D3

R/W

D2

A1

D1

D0

MISO

MOSI

Address

Data

Note

Read operation: R/W bit = 0; Write operation: R/W = 1.

Condition

Name

Definition

33742 Reset

POR

Power-ON Reset

33742 Mode

Transition

NR2R

Normal Request to Reset Mode

NR2N

Normal Request to Normal Mode

NR2STB

Normal Request to Standby Mode

N2R

Normal to Reset Mode

STB2R

Standby to Reset Mode

STO2R

Stop to Reset Mode

STO2NR

Stop to Normal Request

33742 Mode

RESET

33742 in Reset Mode

Table 9. List of Registers

Register

Address

Formal Name

and Link

Comment and Use

Write

Read

MCR

$000

Mode Control Register (MCR)

on page 39

Selection for Normal, Standby, Sleep,

Stop, and Debug modes

BATFAIL, general failure, V

DD

pre-

warning, and Watchdog flag

RCR

$001

Reset Control Register (RCR)

on page 40

Configuration for reset voltage level, CAN Sleep and Stop modes

CAN

$010

CAN Register (CAN) on page

40

CAN slew rate, Sleep and Wake-Up

enable/disable modes, drive enable after

failure

CAN wake-up and CAN failure status bits

IOR

$011

Input/Output Register (IOR)

on page 41

HS (High Side switch) control in Normal

and Standby mode

HS overtemperature bit, V

SUP

, and V2

Low status

WUR

$100

Wake-Up Register (WUR) on

page 42

Control of wake-up input polarity

Wake-up input and real time Lx input state

TIM

$101

Timing Register (TIM1/2) on

page 43

TIM1: Watchdog timing control,

Watchdog Window (WDW) or

Watchdog Timeout (WTO) mode

TIM2: Cyclic Sense and Forced

Wake-Up timing selection

CANL and TXD failure reporting

LPC

$110

Low Power Control Register

(LPC) on page 44

Control HS periodic activation in Sleep

and Stop modes, Forced Wake-Up mode

activation, CAN-INT mode selection

CANH and RXD failure reporting

INTR

$111

Interrupt Register (INTR) on

page 45

Enable or Disable of Interrupts

Interrupt source

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 33793 | Distributed System Interface (DSI) Sensor Interface |

| 33887 | 5.0 A H-Bridge with Load Current Feedback |

| 33888 | Quad High-Side and Octal Low-Side Switch for Automotive |

| 33888A | Quad High-Side and Octal Low-Side Switch for Automotive |

| 338FP-M | Versatile Miniature Switch, High Performance |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 33-7435 | 制造商:Distributed By MCM 功能描述:High Performance LNB |

| 337439-000 | 制造商:TE Connectivity 功能描述:55/0314-26-9CS2793 - Cable Rools/Shrink Tubing |

| 337445 | 制造商:Whirlpool 功能描述:SUPPORT |

| 33-745 | 制造商:MCM 功能描述:DETACHED FERRULE F TYPE CONNECTORS, CABLE TYPE: RG-6, PLATING: NICKEL, USED FOR: ANTENNA AND CABLE TV APPLICATIONS, FOR USE WITH: HEX CRIMP TOOL 22-100, QUANTITY: MINIMUM TEN |

| 3-374595-0 | 功能描述:手工工具 INDENTOR RoHS:否 制造商:Molex 產(chǎn)品:Extraction Tools 類型: 描述/功能:Extraction tool |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。