- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358627 > 33742S (Motorola, Inc.) System Basis Chip (SBC) with Enhanced High-Speed CAN Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | 33742S |

| 廠商: | Motorola, Inc. |

| 元件分類: | CAN |

| 英文描述: | System Basis Chip (SBC) with Enhanced High-Speed CAN Transceiver |

| 中文描述: | 系統(tǒng)基礎(chǔ)芯片的增強(qiáng)型(SBC)的高速CAN收發(fā)器 |

| 文件頁(yè)數(shù): | 22/52頁(yè) |

| 文件大?。?/td> | 1087K |

| 代理商: | 33742S |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

33742

22

MOTOROLA ANALOG INTEGRATED CIRCUIT DEVICE DATA

If no MCU wake-up occurs within the watchdog timing the

33742 activates the

RST

terminal and jumps into the Normal

Request mode. The MCU can then be initialized.

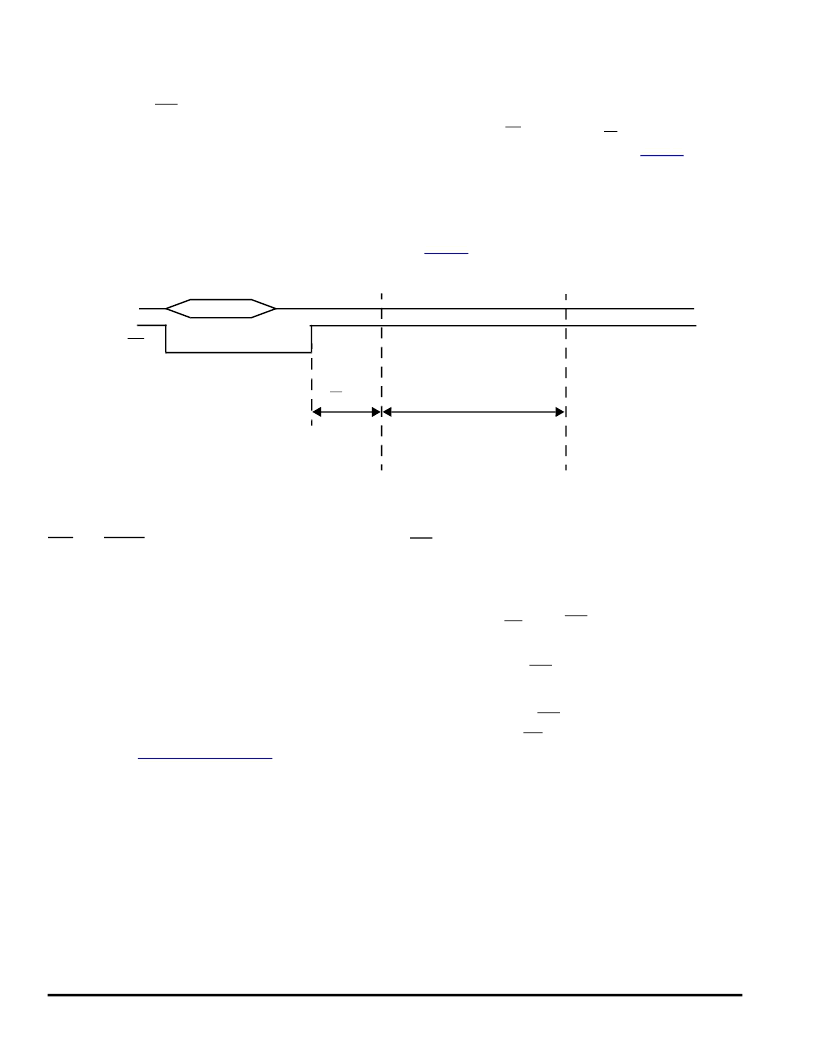

Stop Mode Enter Command

Stop mode is entered at the end of the SPI message at the

rising edge of the

CS

. (Refer to the t

CS-STOP

data in the

Dynamic Electrical Characteristics table on

page 13

.) Once

Stop mode is entered, the 33742 can wake up from the V

DD

regulator overcurrent detection. In order to allow time for the

MCU to complete the last CPU instruction, allowing the MCU to

enter its low power mode, a deglitcher time of 40

μ

s typical is

implemented.

Figure 8

, page 22, depicts the operation of entering the Stop

mode.

Figure 8. Entering Stop Mode

RST

and

WDOG

Terminals, Software Watchdog

Operations

Watchdog Software (Selectable Watchdog

Window or

Watchdog Timeout)

Watchdog software is used in the 33742 Normal and

Standby modes for monitoring the MCU. Watchdog may be

either watchdog window or watchdog timeout, selectable by

SPI (TIM1 subregister, bit WDW). Default is watchdog window.

The watchdog period may be set from 10 ms to 350 ms

(TIM1 subregister, bits WDT0 and WDT1). When watchdog

window is selected, the closed window is the first part of the

selected period, and the open window is the second part of the

period. (Refer to

Timing Register (TIM1/2)

beginning on

page 43.)

Watchdog can only be cleared within the open window time.

Any attempt to clear watchdog in the closed window will

generate a reset. Watchdog is cleared through SPI by

addressing the TIM1 subregister.

RST

Terminal Description

A reset output is available to reset the MCU. Causes of reset

are the following:

V

DD

Falling Out of Range—If V

DD

falls below the reset

threshold (V

RSTTH

), the

RST

terminal is pulled LOW until

V

DD

returns to the normal voltage.

Power-ON Reset—At 33742 power-on or wake-up from

Sleep mode, the

RST

terminal is maintained LOW until

V

DD

is within its operation range.

Watchdog Timeout—If watchdog is not cleared, the

33742 will pull the

RST

terminal LOW for the duration of

the reset time

(

t

RSTDUR

).

SPI CS

SPI Stop/Sleep

Command

33742 in Normal

or Standby mode

33742 in Stop mode.

No I

DD

over I

DD-DGLT

33742 in Stop mode.

I

DD

over I

DD-DGLT

t

CS

-STOP

t

IDD-DGLT

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 33793 | Distributed System Interface (DSI) Sensor Interface |

| 33887 | 5.0 A H-Bridge with Load Current Feedback |

| 33888 | Quad High-Side and Octal Low-Side Switch for Automotive |

| 33888A | Quad High-Side and Octal Low-Side Switch for Automotive |

| 338FP-M | Versatile Miniature Switch, High Performance |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 33-7435 | 制造商:Distributed By MCM 功能描述:High Performance LNB |

| 337439-000 | 制造商:TE Connectivity 功能描述:55/0314-26-9CS2793 - Cable Rools/Shrink Tubing |

| 337445 | 制造商:Whirlpool 功能描述:SUPPORT |

| 33-745 | 制造商:MCM 功能描述:DETACHED FERRULE F TYPE CONNECTORS, CABLE TYPE: RG-6, PLATING: NICKEL, USED FOR: ANTENNA AND CABLE TV APPLICATIONS, FOR USE WITH: HEX CRIMP TOOL 22-100, QUANTITY: MINIMUM TEN |

| 3-374595-0 | 功能描述:手工工具 INDENTOR RoHS:否 制造商:Molex 產(chǎn)品:Extraction Tools 類型: 描述/功能:Extraction tool |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。