- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F800C3 (INTEL CORP) 3 Volt Advanced Boot Block Flash Memory(3 V 高級快速引導(dǎo)塊閃速存儲器) PDF資料下載

參數(shù)資料

| 型號: | 28F800C3 |

| 廠商: | INTEL CORP |

| 元件分類: | DRAM |

| 英文描述: | 3 Volt Advanced Boot Block Flash Memory(3 V 高級快速引導(dǎo)塊閃速存儲器) |

| 中文描述: | 16M X 8 FLASH 3V PROM |

| 文件頁數(shù): | 9/59頁 |

| 文件大小: | 321K |

| 代理商: | 28F800C3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

E

28F800C3, 28F160C3, 28F320C3

9

PRELIMINARY

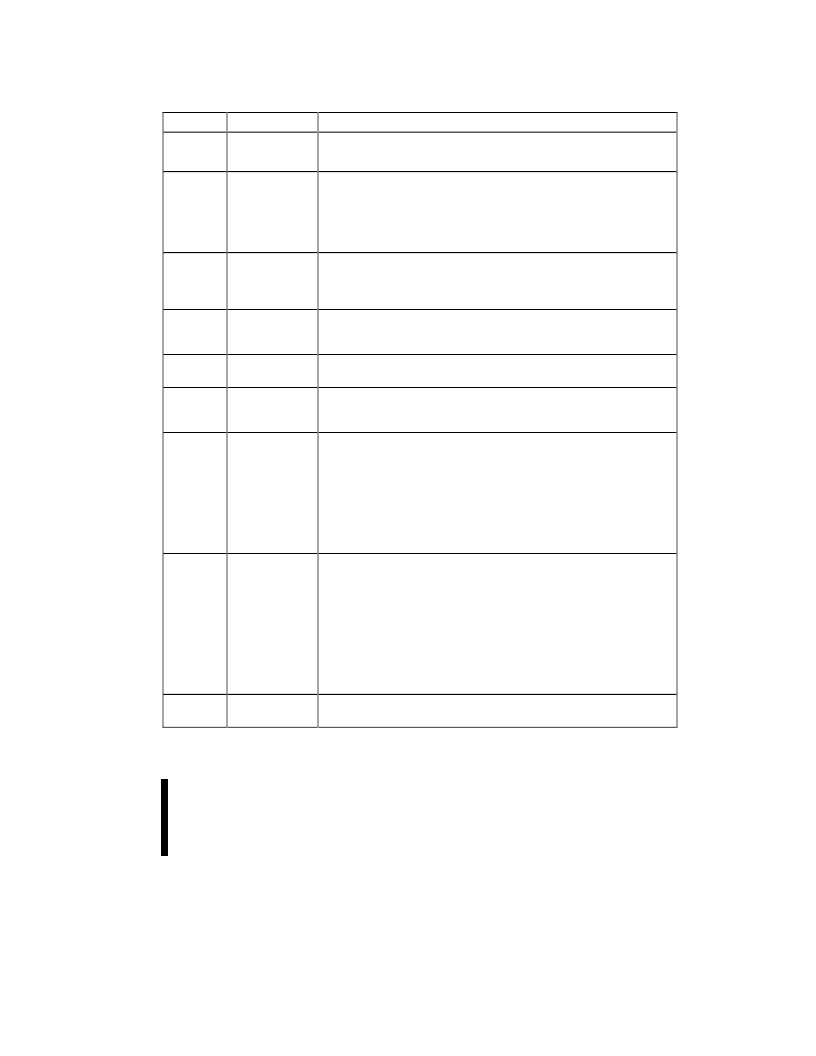

Table 2. 3 Volt Advanced+ Boot Block Pin Descriptions

Symbol

Type

Name and Function

A

0

–A

21

INPUT

ADDRESS INPUTS:

Memory addresses are internally latched during a

program or erase cycle.

8-Mbit: A[0-18], 16-Mbit: A[0-19], 32-Mbit: A[0-20]

DATA INPUTS/OUTPUTS:

Inputs array data on the second CE# and

WE# cycle during a Program command. Inputs commands to the

Command User Interface when CE# and WE# are active. Data is

internally latched. Outputs array, configuration and status register data.

The data pins float to tri-state when the chip is de-selected or the outputs

are disabled.

DQ

0

–DQ

7

INPUT/OUTPUT

DQ

8

–DQ

15

INPUT/OUTPUT

DATA INPUTS/OUTPUTS:

Inputs array data on the second CE# and

WE# cycle during a Program command. Data is internally latched.

Outputs array and configuration data. The data pins float to tri-state when

the chip is de-selected.

CE#

INPUT

CHIP ENABLE:

Activates the internal control logic, input buffers,

decoders and sense amplifiers. CE# is active low. CE# high de-selects

the memory device and reduces power consumption to standby levels.

OE#

INPUT

OUTPUT ENABLE:

Enables the device’s outputs through the data

buffers during a read operation. OE# is active low.

WE#

INPUT

WRITE ENABLE:

Controls writes to the command register and memory

array. WE# is active low. Addresses and data are latched on the rising

edge of the second WE# pulse.

RP#

INPUT

RESET/DEEP POWER-DOWN:

Uses two voltage levels (V

IL

, V

IH

) to

control reset/deep power-down mode.

When RP# is at logic low, the device is in reset/deep power-down

mode

, which drives the outputs to High-Z, resets the Write State

Machine, and minimizes current levels (I

CCD

).

When RP# is at logic high, the device is in standard operation

.

When RP# transitions from logic-low to logic-high, the device resets all

blocks to locked and defaults to the read array mode.

WP#

INPUT

WRITE PROTECT:

Controls the lock-down function of the flexible

Locking feature.

When WP# is a logic low, the lock-down mechanism is enabled

and

blocks marked lock-down cannot be unlocked through software.

When WP# is logic high, the lock-down mechanism is disabled

and

blocks previously locked-down are now locked and can be unlocked and

locked through software. After WP# goes low, any blocks previously

marked lock-down revert to that state.

See Section 3.3 for details on block locking.

V

CC

SUPPLY

DEVICE POWER SUPPLY:

[2.7 V–3.6 V] Supplies power for device

operations.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F160C3 | 3 Volt Advanced Boot Block Flash Memory(3 V 高級快速引導(dǎo)塊閃速存儲器) |

| 28F320D18 | 1.8 Volt Intel Dual-Plane Flash Memory(1.8 V Intel 雙平面閃速存儲器) |

| 28F320J5 | 5 Volt Intel StrataFlash Memory(5 V 32M位英特爾StrataFlash存儲器) |

| 28F640J5 | 5 V Intel StrataFlash Memory(5V 64M位英特爾StrataFlash閃速存儲器) |

| 28F400B3 | SMART 3 ADVANCED BOOT BLOCK WORD-WIDE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F800CE-T/B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Boot Flash |

| 28F800CV-T/B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-MBIT (512K X 16. 1024K X 8) SmartVoltage BOOT BLOCK FLASH MEMORY FAMILY |

| 28F800F3 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:FAST BOOT BLOCK FLASH MEMORY FAMILY 8 AND 16 MBIT |

| 28FAN2500_AAA3A862 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| 28FAN2502_AAA3A862 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。