- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F320W30 (Intel Corp.) 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) PDF資料下載

參數(shù)資料

| 型號: | 28F320W30 |

| 廠商: | Intel Corp. |

| 元件分類: | DRAM |

| 英文描述: | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 中文描述: | 1.8伏英特爾無線閃存的3伏的I / O和SRAM(寬30) |

| 文件頁數(shù): | 24/82頁 |

| 文件大小: | 749K |

| 代理商: | 28F320W30 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

28F6408W30, 28F3204W30, 28F320W30, 28F640W30

18

Preliminary

As an example, a clock frequency of 52 MHz will be used. The clock period is 19.2 ns. This data is

applied to the formula above for the subsequent reads assuming the data output hold time is one

clock:

14 ns + 4 ns

≤

19.2 ns

This equation is satisfied and data output will be available and valid at every clock period.

If t

DATA

is long, hold for two cycles.

Now assume the clock frequency is 66 MHz. This corresponds to a 15 ns period. The initial access

time is calculated to be 80 ns (LC 4). This condition satisfies t

AVQV

(ns) + t

ADD-DELAY

(ns) +

t

DATA

(ns) = 70 ns + 6 ns + 4 ns = 80 ns, as shown above in the First Access Latency Count

equations. However, the data output hold time of one clock violates the one-clock data hold

condition:

t

CHQV

(ns) + t

DATA

(ns)

≤

One CLK Period

14 ns + 4 ns = 18 ns is not less than one clock period of 15 ns. To satisfy the formula above, the

data output hold time must be set at 2 clocks to correctly allow for data output setup time. This

formula is also satisfied if the CPU has t

DATA

(ns)

≤

1 ns, which yields:

14 ns + 1 ns

≤

15 ns

In page mode reads, the initial access time can be determined by the formula:

t

ADD-DELAY

(ns) + t

DATA

(ns) + t

AVQV

(ns)

and subsequent reads in page mode are defined by:

t

APA

(ns) + t

DATA

(ns)

(minimum time)

4.2.6

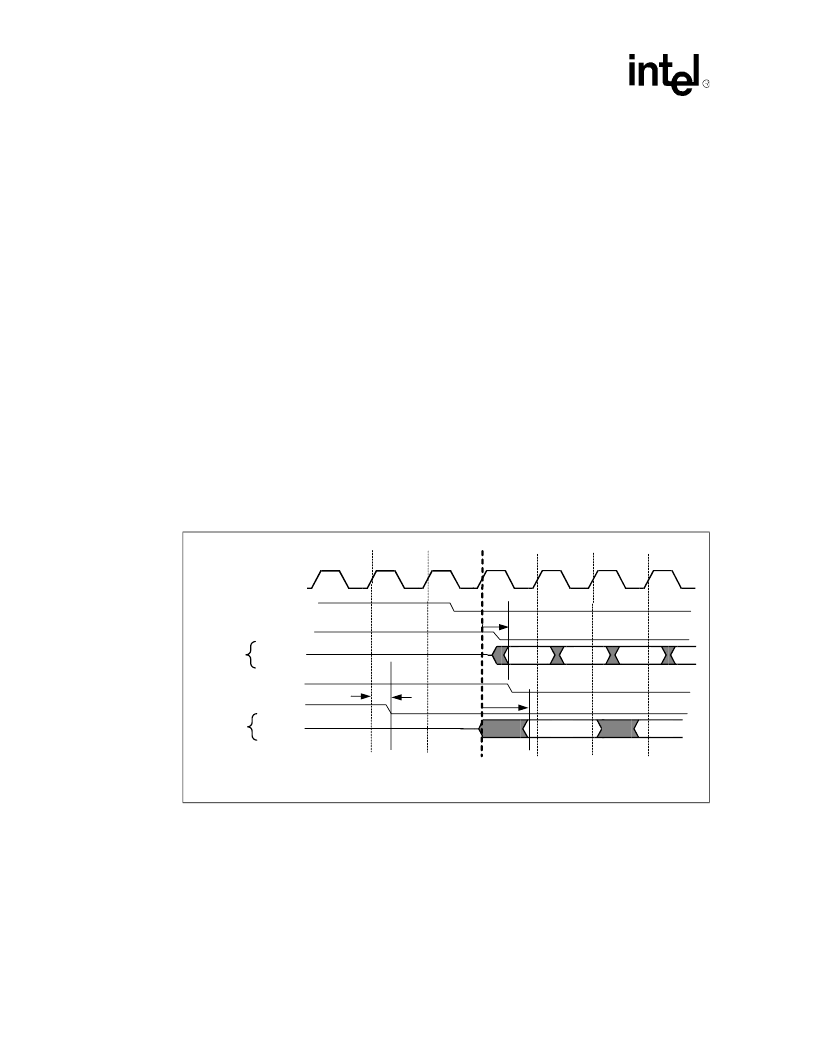

WAIT Configuration (WC)

CR.8 sets the WAIT signal delay. The WAIT signal delay determines when the WAIT signal is

asserted. The WAIT signal can be asserted either one clock before or at the time of the misaligned

16-word boundary crossing. An asserted WAIT signal indicates invalid data on the data bus.

Figure 8. Data Output Configuration with WAIT Signal Delay

DQ

15-0

[Q]

CLK [C]

Valid

Output

Valid

Output

Valid

Output

DQ

15-0

[Q]

Valid

Output

Valid

Output

1 CLK

Data Hold

WAIT (CR.8 = 1)

WAIT (CR.8 = 0)

t

CHQV

t

CHQV

WAIT (CR.8 = 0)

WAIT (CR.8 = 1)

2 CLK

Data Hold

t

CHTL/H

Note 1

Note 1

Note 1

Note 1

Note1: WAIT shown active high (CR.10 = 1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F6408W30 | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 28F640W30 | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 28F320B3 | SMART 3 ADVANCED BOOT BLOCK 4-, 8-, 16-, 32-MBIT FLASH MEMORY FAMILY |

| 28F640P3 | Intel StrataFlash Embedded Memory |

| 28F320C3 | 3 Volt Advanced Boot Block Flash Memory(3 V 高級快速引導(dǎo)塊閃速存儲器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F400B3 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SMART 3 ADVANCED BOOT BLOCK WORD-WIDE |

| 28F400B5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SMART 5 BOOT BLOCK. FLASH MEMORY FAMILY 2. 4. 8 MBIT |

| 28F400B5WG8BET | 制造商: 功能描述: 制造商:Micron Technology Inc 功能描述: 制造商:undefined 功能描述: |

| 28F400BL-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-MBlT (256K x 16. 512K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F400BL-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-MBlT (256K x 16. 512K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。