- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F320W30 (Intel Corp.) 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) PDF資料下載

參數(shù)資料

| 型號: | 28F320W30 |

| 廠商: | Intel Corp. |

| 元件分類: | DRAM |

| 英文描述: | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 中文描述: | 1.8伏英特爾無線閃存的3伏的I / O和SRAM(寬30) |

| 文件頁數(shù): | 15/82頁 |

| 文件大小: | 749K |

| 代理商: | 28F320W30 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

28F6408W30, 28F3204W30, 28F320W30, 28F640W30

Preliminary

9

3.0

Product Operations

3.1

Bus Operations

The 1.8 Volt Intel

Wireless Flash Memory

’

s on-chip Write State Machine (WSM) manages erase

and program algorithms. The local CPU controls the in-system read, program, and erase operations

of the flash device. Bus cycles to and from the flash device conform to standard microprocessor

bus operations. RST#, CE#, OE#, WE#, and ADV# signals control the flash. WAIT informs the

CPU of valid data during burst reads. S-OE#, S-WE#, S-CS

1

#, S-CS

2

, S-LB# and S-UB# control

the SRAM. S-UB# and S-LB# must be tied together to restrict x16 mode.

Table 3

summarizes bus

operations.

NOTES:

1. Manufacturer and device ID codes are accessed by Read ID Register command.

2. Query and status register accesses use only DQ

. All other accesses use DQ

15-0

.

3. X must be V

or V

for control signals and addresses.

4. Refer to

Table 5,

“

Command Bus Definitions

”

on page 11

for valid D

IN

during a write operation.

5. Two devices may not drive the memory bus at the same time.

6. The SRAM can be placed into data retention mode by lowering the S-V

CC

to the V

DR

limit when in standby

mode.

7. Always tie S-UB# and S-LB# together.

3.2

Flash Command Definitions

Device operations are selected by writing specific commands to the Command User Interface

(CUI).

Table 4,

“

Command Code and Descriptions

”

on page 10

lists all possible command codes

and descriptions.

Table 5,

“

Command Bus Definitions

”

on page 11

further defines command bus

cycle operations. Since commands are partition-specific, it is important to write commands within

the target partition range.

Multi-cycle command writes to the flash memory partition must be issued sequentially without

intervening command writes. For example, an Erase Setup command to partition X must be

immediately followed by the Erase Confirm command in order to be executed properly. The

address given during the Erase Confirm command determines the location of the erase. If the Erase

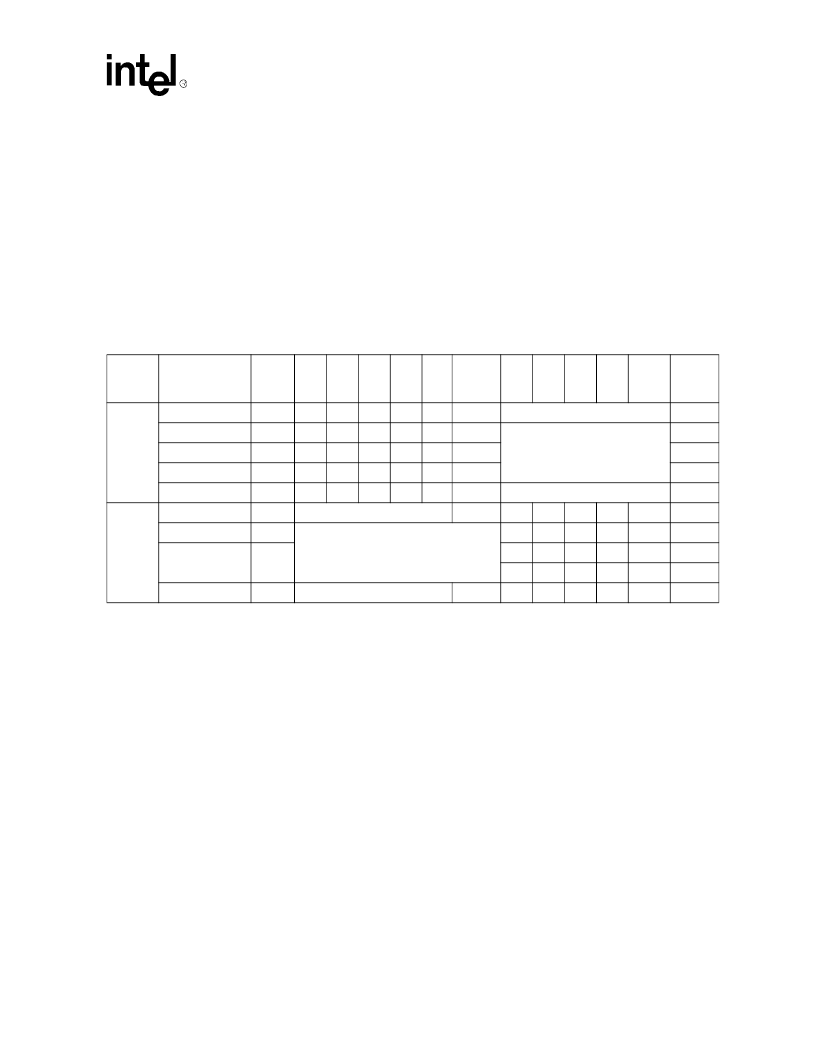

Table 3. Bus Operations

M

N

R

C

O

W

A

W

S

1

#

S

2

S

S

S

S

7

D

[

FLASH

Read

1,2, 5

V

IH

V

IL

V

IL

V

IH

V

IL

Valid

SRAM must be in High-Z

D

OUT

Output Disable

3

V

IH

V

IL

V

IH

V

IH

X

High-Z

Any Valid SRAM Mode

High-Z

Standby

3

V

IH

V

IH

X

X

X

High-Z

High-Z

Reset

3

V

IL

X

X

X

X

High-Z

High-Z

Write

4, 5

V

IH

V

IL

V

IH

V

IL

V

IL

High-Z

SRAM must be in High Z

D

IN

SRAM

Read

5

Flash must be in High-Z

High-Z

V

IL

V

IH

V

IL

V

IH

V

IL

D

OUT

Output Disable

3

Any Valid FLASH Mode

V

IL

V

IH

V

IH

V

IH

X

High-Z

Standby and

Data Retention

3, 6

V

IH

X

X

X

X

High-Z

X

V

IL

X

X

X

High-Z

Write

5

Flash must be in High-Z

High-Z

V

IL

V

IH

V

IH

V

IL

V

IL

D

IN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F6408W30 | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 28F640W30 | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 28F320B3 | SMART 3 ADVANCED BOOT BLOCK 4-, 8-, 16-, 32-MBIT FLASH MEMORY FAMILY |

| 28F640P3 | Intel StrataFlash Embedded Memory |

| 28F320C3 | 3 Volt Advanced Boot Block Flash Memory(3 V 高級快速引導(dǎo)塊閃速存儲器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F400B3 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SMART 3 ADVANCED BOOT BLOCK WORD-WIDE |

| 28F400B5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SMART 5 BOOT BLOCK. FLASH MEMORY FAMILY 2. 4. 8 MBIT |

| 28F400B5WG8BET | 制造商: 功能描述: 制造商:Micron Technology Inc 功能描述: 制造商:undefined 功能描述: |

| 28F400BL-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-MBlT (256K x 16. 512K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

| 28F400BL-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-MBlT (256K x 16. 512K x 8) LOW-POWER BOOT BLOCK FLASH MEMORY FAMILY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。