- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368731 > 16F628 (Microchip Technology Inc.) CAT 5E CROSSOVER PATCH CORD CABLE BLUE 1 FT PDF資料下載

參數(shù)資料

| 型號(hào): | 16F628 |

| 廠商: | Microchip Technology Inc. |

| 英文描述: | CAT 5E CROSSOVER PATCH CORD CABLE BLUE 1 FT |

| 中文描述: | 基于閃存的8位CMOS微控制器 |

| 文件頁(yè)數(shù): | 59/168頁(yè) |

| 文件大?。?/td> | 3760K |

| 代理商: | 16F628 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)當(dāng)前第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)

2002 Microchip Technology Inc.

Preliminary

DS40044A-page 57

PIC16F627A/628A/648A

9.2.1

CCP PIN CONFIGURATION

The user must configure the RB3/CCP1 pin as an out-

put by clearing the TRISB<3> bit.

9.2.2

TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchro-

nized Counter mode if the CCP module is using the

compare feature. In Asynchronous Counter mode, the

compare operation may not work.

9.2.3

SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1

pin is not affected. Only a CCP interrupt is generated (if

enabled).

9.2.4

SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated

which may be used to initiate an action.

The special event trigger output of CCP1 resets the

TMR1 register pair. This allows the CCPR1 register to

effectively be a 16-bit programmable period register for

Timer1.

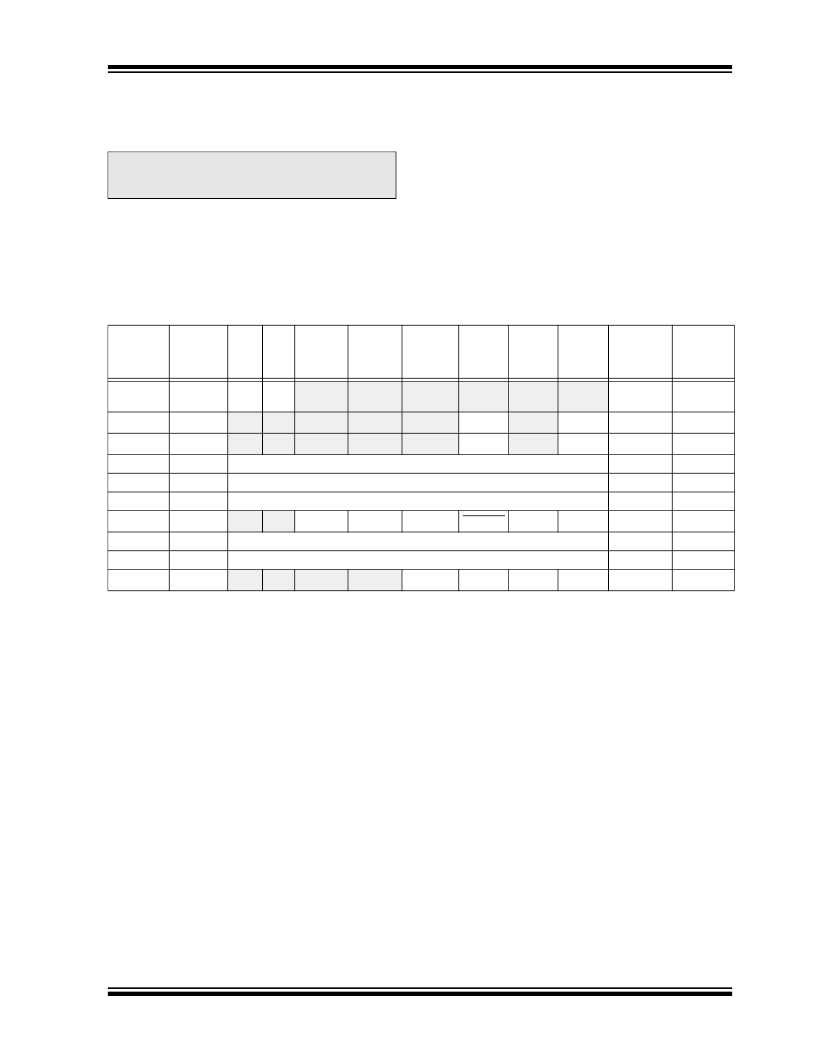

TABLE 9-2:

REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

Note:

Clearing the CCP1CON register will force

the RB3/CCP1 compare output latch to the

default low level. This is not the data latch.

Address

Name

Bit 7 Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on

POR

Value on

all other

RESETS

0Bh, 8Bh,

10Bh, 18Bh

INTCON

GIE

PEIE

T0IE

INTE

RBIE

T0IF

INTF

RBIF

0000 000x 0000 000u

0Ch

PIR1

EEIF CMIF

RCIF

TXIF

—

CCP1IF

TMR2IF

TMR1IF

0000 -000 0000 -000

8Ch

PIE1

EEIE CMIE

RCIE

TXIE

—

CCP1IE

TMR2IE

TMR1IE

0000 -000 0000 -000

86h, 186h

TRISB

PORTB Data Direction Register

1111 1111 1111 1111

0Eh

TMR1L

Holding register for the Least Significant Byte of the 16-bit TMR1 register

xxxx xxxx uuuu uuuu

0Fh

TMR1H

Holding register for the Most Significant Byte of the 16-bit TMR1register

xxxx xxxx uuuu uuuu

10h

T1CON

—

—

T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON

--00 0000 --uu uuuu

15h

CCPR1L

Capture/Compare/PWM register1 (LSB)

xxxx xxxx uuuu uuuu

16h

CCPR1H

Capture/Compare/PWM register1 (MSB)

xxxx xxxx uuuu uuuu

17h

CCP1CON

—

—

CCP1X

CCP1Y

CCP1M3

CCP1M2 CCP1M1 CCP1M0

--00 0000 --00 0000

Legend:

x

= unknown,

u

= unchanged,

-

= unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 16M0 | PC SERIAL MODEM CBL 50 FT |

| 16M0B | APPLE IIC CABLE TO IWRTR MODEM |

| 16M0BC | KEYBD.EXT. MINI DIN 4 MM 6 FT |

| 16M0BS | KEYBD.EXT. MINI DIN 4 MM 10 FT |

| 16M0D | MINI DIN 8, MALE-MALE 10 FT. |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 16F630 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:14-Pin FLASH-Based 8-Bit CMOS Microcontrollers |

| 16F684-I | 制造商:Microchip Technology Inc 功能描述: |

| 16F6H | 制造商:EDAL 制造商全稱:EDAL 功能描述:Silicon High Voltage Assembly |

| 16F6H1 | 制造商:EDAL 制造商全稱:EDAL 功能描述:Silicon High Voltage Assembly |

| 16F7674 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SMD TWEEZER HEAD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。