- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373784 > ZL30410 (Zarlink Semiconductor Inc.) CONN HDR INVERSE 30POS 5ROW VERT PDF資料下載

參數(shù)資料

| 型號: | ZL30410 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | CONN HDR INVERSE 30POS 5ROW VERT |

| 中文描述: | 多業(yè)務(wù)線卡鎖相環(huán) |

| 文件頁數(shù): | 1/38頁 |

| 文件大?。?/td> | 400K |

| 代理商: | ZL30410 |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2003, Zarlink Semiconductor Inc. All Rights Reserved.

Features

Generates clocks for OC-3, STM-1, DS3, E3,

DS2, DS1, E1, 19.44 MHz and ST-BUS

Meets jitter generation requirements for STM-1,

OC-3, DS3, E3, J2 (DS2), E1 and DS1 interfaces

Compatible with GR-253-CORE SONET stratum

3 and G.813 SEC timing compliant clocks

Provides “hit-less” reference switching

Detects frequency of both reference clocks and

synchronizes to any combination of 8 kHz, 1.544

MHz, 2.048 MHz and 19.44 MHz reference

frequencies

Continuously monitors both references for

frequency accuracy exceeding ±12 ppm

Holdover accuracy of 70x10

-12

meets GR-1244

Stratum 3E and ITU-T G.812 requirements

Meets requirements of G.813 Option 1 for SDH

Equipment Clocks (SEC) and GR-1244 for

Stratum 4E and Stratum 4 Clocks

3.3V power supply

Applications

Line Card synchronization for SDH, SONET, DS3,

E3, J2 (DS2), E1 and DS1 interfaces

Timing card synchronization for SDH and PDH

Network Elements

Clock generation for ST-BUS and GCI timing

Description

The

Phase-Locked Loop designed to generate multiple

clocks for SONET, SDH and PDH equipment including

timing for ST-BUS and GCI interfaces.

ZL30410

is

a

Multi-service

Line

Card

The ZL30410 operates in NORMAL (LOCKED),

HOLDOVER and FREE-RUN modes to ensure that in

the presence of jitter and interruptions to the reference

signals, the generated clocks meet international

standards. The filtering characteristics of the PLL are

hardware pin selectable and they do not require any

external adjustable components. The ZL30410 uses an

external 20 MHz Master Clock Oscillator to provide a

stable timing source for the HOLDOVER operation.

November 2003

Ordering Information

ZL30410QCC

80 Pin LQFP

-40

°

C to 85

°

C

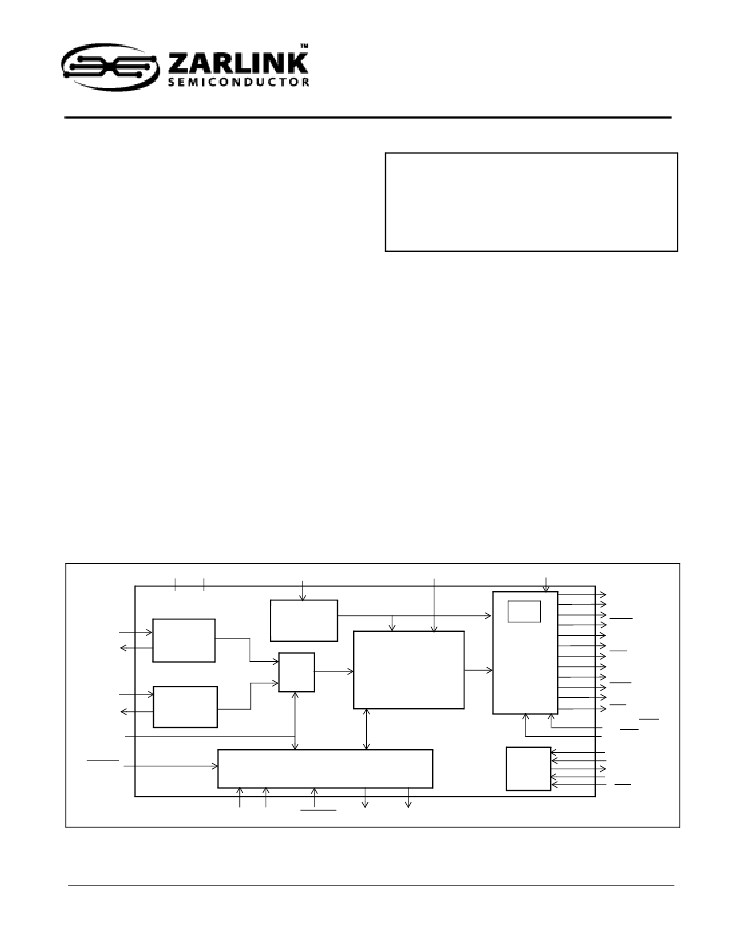

Figure 1 - Functional Block Diagram

Zarlink Semiconductor US Patent No. 5,602,884, UK Patent No. 0772912,

France Brevete S.G.D.G. 0772912; Germany DBP No. 69502724.7-08

Control State Machine

MUX

Primary

Acquisition

PLL

MS1 MS2

RESET

SEC

Trst

C19o

C16o

C8o

C6o

C34/C44

C4o

C2o

C1.5o

F16o

F8o

F0o

PRI

HOLDOVER

LOCK

PRIOR

C155P/N

E3DS3/OC3

E3/DS3

Secondary

Acquisition

PLL

RefAlign

JTAG

IEEE

1149.1a

Master Clock

Frequency

Calibration

APLL

SECOR

Tms

Tdo

Tclk

Clock

Synthesizer

Core PLL

RefSel

FCS

C20i

VDD GND

OE

07

ZL30410

Multi-service Line Card PLL

Data Sheet

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL30410QCC | CONN SOCKET R/A 4R0W 24POS SLD |

| ZL30414 | SONET/SDH Clock Multiplier PLL |

| ZL30414QGC | SONET/SDH Clock Multiplier PLL |

| ZL30414QGC1 | SONET/SDH Clock Multiplier PLL |

| ZL30415 | SONET/SDH Clock Multiplier PLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30410_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Multi-service Line Card PLL |

| ZL30410QCC | 制造商:Microsemi Corporation 功能描述:PLL CLOCK GEN SGL UP TO 19.44MHZ 80LQFP EP - Trays |

| ZL30410QCC1 | 制造商:Microsemi Corporation 功能描述: |

| ZL30410QCG1 | 制造商:Microsemi Corporation 功能描述:IC SONET/SDH NETWORK ELEMENT PLL 制造商:Microsemi Corporation 功能描述:LEAD FREE SONET/SDH NETWORK ELEMENT PLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC PLL SONET/SDH/PDH 80LQFP 制造商:Microsemi Corporation 功能描述:IC PLL SONET/SDH/PDH 80LQFP |

| ZL30414 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH Clock Multiplier PLL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。