- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1975 > XR16M598IQ100-F (Exar Corporation)IC UART FIFO 16B OCTAL 100QFP PDF資料下載

參數(shù)資料

| 型號: | XR16M598IQ100-F |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 31/58頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC UART FIFO 16B OCTAL 100QFP |

| 標(biāo)準(zhǔn)包裝: | 66 |

| 特點(diǎn): | * |

| 通道數(shù): | 8 |

| FIFO's: | 16 字節(jié) |

| 規(guī)程: | RS485 |

| 電源電壓: | 1.62 V ~ 3.63 V |

| 帶自動(dòng)流量控制功能: | 是 |

| 帶IrDA 編碼器/解碼器: | 是 |

| 帶故障啟動(dòng)位檢測功能: | 是 |

| 帶調(diào)制解調(diào)器控制功能: | 是 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-BQFP |

| 供應(yīng)商設(shè)備封裝: | 100-QFP(14x20) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

XR16M598

37

REV. 1.0.0

1.62V TO 3.63V HIGH PERFORMANCE OCTAL UART WITH 16-BYTE FIFO

FCR[5:4]: Transmit FIFO Trigger Select

(logic 0 = default, TX trigger level = 1)

These 2 bits set the trigger level for the transmit FIFO interrupt. The UART will issue a transmit interrupt when

the number of characters in the FIFO falls below the selected trigger level, or when it gets empty in case that

the FIFO did not get filled over the trigger level on last re-load. Table 15 below shows the selections.

FCR[3]: DMA Mode Select

This bit has no effect since TXRDY and RXRDY pins are not available in this device. It is provided for legacy

software compatibility.

Logic 0 = Set DMA to mode 0 (default).

Logic 1 = Set DMA to mode 1.

FCR[2]: TX FIFO Reset

This bit is only active when FCR bit-0 is active.

Logic 0 = No transmit FIFO reset (default).

Logic 1 = Reset the transmit FIFO pointers and FIFO level counter logic (the transmit shift register is not

cleared or altered). This bit will return to a logic 0 after resetting the FIFO.

FCR[1]: RX FIFO Reset

This bit is only active when FCR bit-0 is active.

Logic 0 = No receive FIFO reset (default).

Logic 1 = Reset the receive FIFO pointers and FIFO level counter logic (the receive shift register is not

cleared or altered). This bit will return to a logic 0 after resetting the FIFO.

FCR[0]: TX and RX FIFO Enable

Logic 0 = Disable the transmit and receive FIFO (default).

Logic 1 = Enable the transmit and receive FIFOs. This bit must be set to logic 1 when other FCR bits are

written or they will not be programmed.

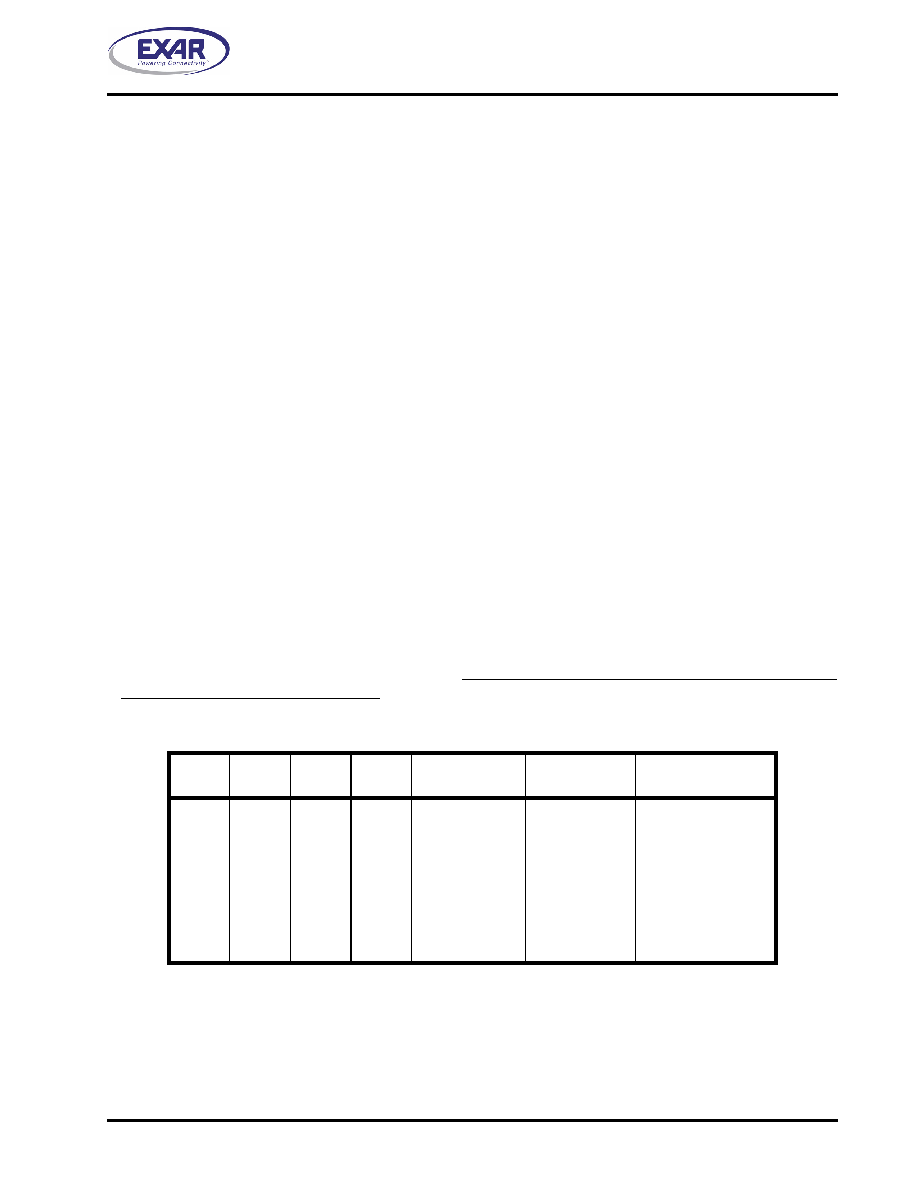

TABLE 15: TRANSMIT AND RECEIVE FIFO TRIGGER TABLE AND LEVEL SELECTION

BIT-7

BIT-6

BIT-5

BIT

-4

RECEIVE TRIGGER

LEVEL

TRANSMIT

TRIGGER LEVEL

COMPATIBILITY

0

1

0

1

0

1

0

1

0

1

0

1

1(default)

4

8

14

1(default)

4

8

14

16C550, 16C2550,

16C2552, 16C554,

16C580 compatible

4.6

Line Control Register (LCR) - Read/Write

The Line Control Register is used to specify the asynchronous data communication format. The word or

character length, the number of stop bits, and the parity are selected by writing the appropriate bits in this

register.

FCR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR16M654IQ100-F | IC UART FIFO 64B QUAD 100QFP |

| XR16M670IL32-F | IC UART FIFO 32B 32QFN |

| XR16M680IM48-F | IC UART FIFO 32B 48TQFP |

| XR16M681IL32-F | IC UART FIFO 64B 32QFN |

| XR16M698IQ100-F | IC UART FIFO 32B OCTAL 100QFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16M654 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V QUAD UART WITH 64-BYTE FIFO |

| XR16M654D | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V QUAD UART WITH 64-BYTE FIFO |

| XR16M654DIV-0A-EVB | 功能描述:界面開發(fā)工具 Eval Board for XR16M654DIV-0A RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR16M654DIV-0B-EVB | 功能描述:界面開發(fā)工具 Eval Board for XR16M654DIV-0B RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR16M654DIV64 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V QUAD UART WITH 64-BYTE FIFO |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。