- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄140360 > W3H32M72E-400SB2M (MICROSEMI CORP-PMG MICROELECTRONICS) 32M X 72 DDR DRAM, 0.6 ns, PBGA208 PDF資料下載

參數(shù)資料

| 型號(hào): | W3H32M72E-400SB2M |

| 廠商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分類: | DRAM |

| 英文描述: | 32M X 72 DDR DRAM, 0.6 ns, PBGA208 |

| 封裝: | 16 X 20 MM, 1 MM PITCH, PLASTIC, BGA-208 |

| 文件頁(yè)數(shù): | 7/25頁(yè) |

| 文件大小: | 1062K |

| 代理商: | W3H32M72E-400SB2M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

W3H32M72E-XSB2X

November 2010 2010 Microsemi Corporation. All rights reserved.

15

Microsemi Corporation (602) 437-1520 www.whiteedc.com

Rev. 3

www.microsemi.com

Microsemi Corporation reserves the right to change products or specications without notice.

Data from any READ burst may be concatenated with data from a

subsequent READ command to provide a continuous ow of data.

The rst data element from the new burst follows the last element

of a completed burst. The new READ command should be issued x

cycles after the rst READ command, where x equals BL / 2 cycles.

WRITE COMMAND

The WRITE command is used to initiate a burst write access to an

active row. The value on the BA1–BA0 inputs selects the bank,

and the address provided on inputs A0–9 selects the starting

column location. The value on input A10 determines whether or

not auto precharge is used. If auto precharge is selected, the

row being accessed will be precharged at the end of the WRITE

burst; if auto precharge is not selected, the row will remain open

for subsequent accesses.

Input data appearing on the DQ is written to the memory array

subject to the DM input logic level appearing coincident with the

data. If a given DM signal is registered LOW, the corresponding

data will be written to memory; if the DM signal is registered HIGH,

the corresponding data inputs will be ignored, and a WRITE will

not be executed to that byte/column location.

WRITE OPERATION

WRITE bursts are initiated with a WRITE command, as shown in

Figure 12. DDR2 SDRAM uses WL equal to RL minus one clock

cycle [WL = RL - 1CK = AL + (CL - 1CK)]. The starting column and

bank addresses are provided with the WRITE command, and auto

precharge is either enabled or disabled for that access. If auto

precharge is enabled, the row being accessed is precharged at the

completion of the burst. For the generic WRITE commands used

in the following illustrations, auto precharge is disabled.

During WRITE bursts, the first valid data-in element will be

registered on the rst rising edge of DQS following the WRITE

command, and subsequent data elements will be registered on

successive edges of DQS. The LOW state on DQS between the

WRITE command and the rst rising edge is known as the write

preamble; the LOW state on DQS following the last data-in element

is known as the write postamble.

The time between the WRITE command and the rst rising DQS

edge is WL ± tDQSS. Subsequent DQS positive rising edges are

timed, relative to the associated clock edge, as ± tDQSS. tDQSS is

specied with a relatively wide range (25 percent of one clock

cycle). All of the WRITE diagrams show the nominal case, and

where the two extreme cases (tDQSS [MIN] and tDQSS [MAX]) might

not be intuitive, they have also been included. Upon completion of

a burst, assuming no other commands have been initiated, the DQ

will remain High-Z and any additional input data will be ignored.

Data for any WRITE burst may be concatenated with a subsequent

WRITE command to provide continuous ow of input data. The rst

data element from the new burst is applied after the last element

of a completed burst. The new WRITE command should be issued

x

cycles after the rst WRITE command, where x equals BL/2.

DDR2 SDRAM supports concurrent auto precharge options, as

shown in Table 4.

DDR2 SDRAM does not allow interrupting or truncating any WRITE

burst using BL = 4 operation. Once the BL = 4 WRITE command is

registered, it must be allowed to complete the entire WRITE burst

cycle. However, a WRITE (with auto precharge disabled) using BL

= 8 operation might be interrupted and truncated ONLY by another

WRITE burst as long as the interruption occurs on a 4-bit boundary,

due to the 4n prefetch architecture of DDR2 SDRAM. WRITE burst

BL = 8 operations may not to be interrupted or truncated with any

command except another WRITE command.

Data for any WRITE burst may be followed by a subsequent READ

command. The number of clock cycles required to meet tWTR is

either 2 or tWTR/tCK, whichever is greater. Data for any WRITE burst

may be followed by a subsequent PRECHARGE command. tWT

starts at the end of the data burst, regardless of the data mask

condition.

PRECHARGE COMMAND

The PRECHARGE command, illustrated in Figure 13, is used

to deactivate the open row in a particular bank or the open row

in all banks. The bank(s) will be available for a subsequent row

activation a specied time (tRP) after the PRECHARGE command

is issued, except in the case of concurrent auto precharge, where

a READ or WRITE command to a different bank is allowed as long

as it does not interrupt the data transfer in the current bank and

does not violate any other timing parameters. Once a bank has

been precharged, it is in the idle state and must be activated prior

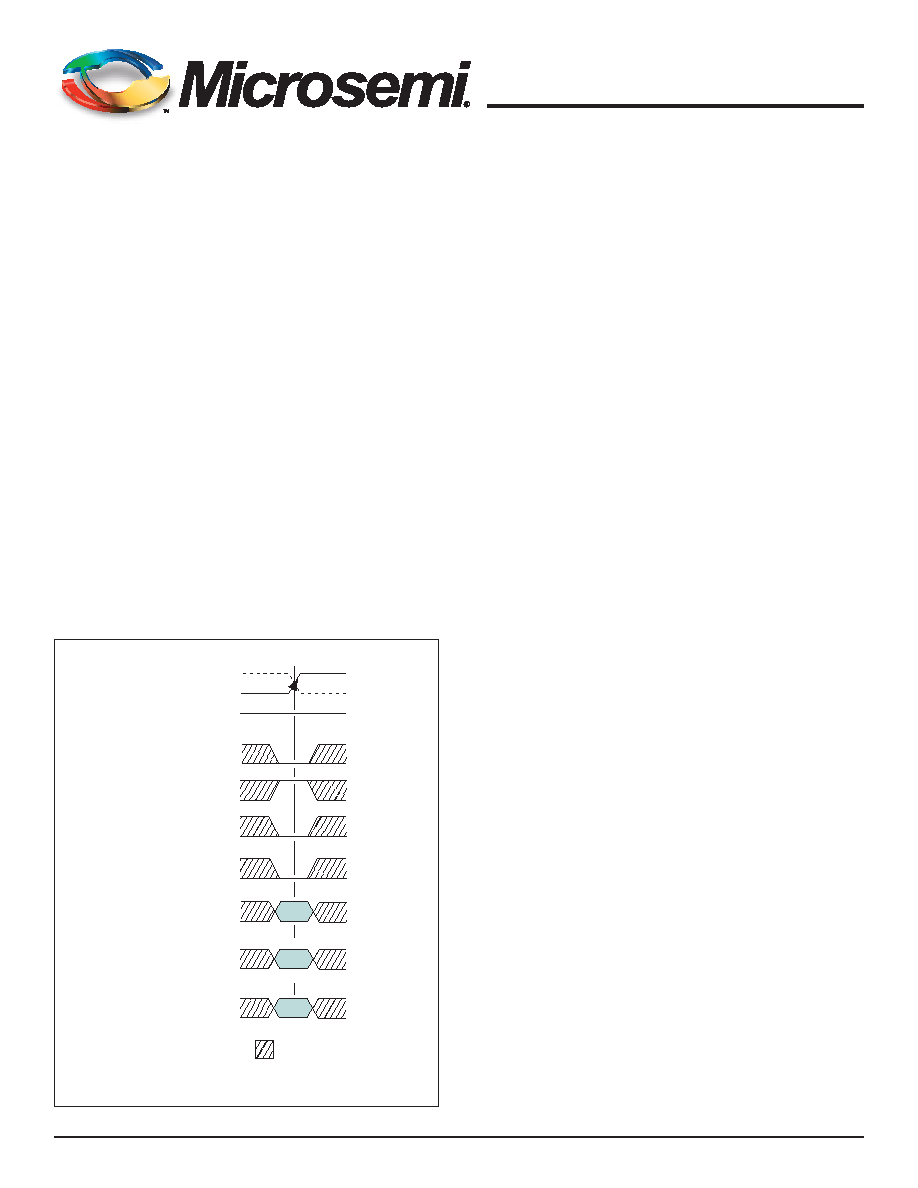

FIGURE 12 – WRITE COMMAND

CS#

WE#

CAS#

RAS#

CKE

CA

A10

BANK ADDRESS

HIGH

EN AP

DIS AP

BA

CK

CK#

DON’T CARE

ADDRESS

Note: CA = column address; BA = bank address; EN AP = enable auto precharge; and

DIS AP = disable auto precharge.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W3HG2128M64EEU805XD4IMG | 256M X 64 DDR DRAM MODULE, 0.4 ns, ZMA200 |

| W7MG21M32SVT70BNC | 2M X 32 FLASH 3.3V PROM MODULE, 70 ns, SMA80 |

| W7NCF02GH30CS2AG | 128M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF02GH30CS5DG | 128M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF02GH30CS8DG | 128M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W3H32M72E-400SBC | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR2, 1.8V, 400MHZ, 208PBGA COMMERICAL TEMP. - Bulk |

| W3H32M72E-400SBI | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR2, 1.8V, 400MHZ, 208PBGA INDUSTRIAL TEMP. - Bulk |

| W3H32M72E-400SBM | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR2, 1.8V, 400MHZ, 208PBGA MIL-TEMP. - Bulk |

| W3H32M72E-533ES | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:32M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H32M72E-533ESC | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:32M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。