- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385949 > TSB42AA9I (Texas Instruments, Inc.) STORAGELYNX 1394 LINK-LAYER CONTROLLER FOR ATA/ATAPI STORAGE PRODUCTS PDF資料下載

參數(shù)資料

| 型號(hào): | TSB42AA9I |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | STORAGELYNX 1394 LINK-LAYER CONTROLLER FOR ATA/ATAPI STORAGE PRODUCTS |

| 中文描述: | STORAGELYNX 1394鏈路層的ATA控制器/ ATAPI儲(chǔ)存產(chǎn)品 |

| 文件頁數(shù): | 27/183頁 |

| 文件大小: | 798K |

| 代理商: | TSB42AA9I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁

32

timing. If the host asserts this signal, the ceLynx asserts the MCIF_ACK pin when

either the data on MCIF_D[15:0] is valid (during a read access) or the data on

MCIF_D[15:0] has been latched (during a write access). As soon as the host

deasserts this signal, the ceLynx deasserts the MCIF_ACK.

Status of the MCIF_CS pin. When this signal is asserted, the MCIF_ACK assumes that

ceLynx is the only peripheral device currently selected on the MCIF interface, and as such,

it drives the MCIF_ACK pin either asserted or deasserted.

Setting of the PINCFG.MCACKZFLT bit at 0x004. When this register bit is set

to 0, the MCIF_ACK signal is always in the high-impedance state and the ceLynx

never asserts the MCIF_ACK pin. The ceLynx never asserts the MCIF_ACK pin.

The user must never set this bit to 0, because this prevents communication with

the host. If this register bit is set to 1 (default), then the MCIF_ACK pin output drivers

are turned off when the pin is deasserted (assuming the MCIF_CS pin is

deasserted).

Setting of MCIFCFG.MCACKZDLY bits at 0x010. These bits work in conjunction

with the MCACKZFLT mode to control the time that the MCIF_ACK pin is

deasserted before the pin output drivers, described previously, are turned off. This

delay can be adjusted from 0 ns (default) up to 10 ns. If the MCACKZFLT register

bit is set to 0, the MCACKZDLY register bits are ignored.

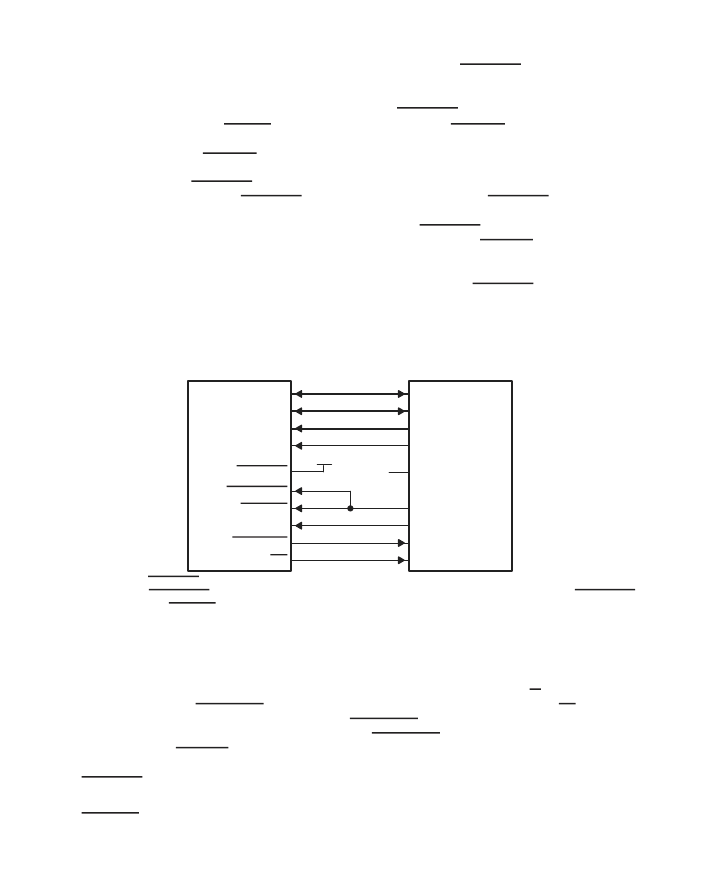

Figure 31 shows the typical connection between ceLynx and a 68000-style processor.

ceLynx

68000-Style

MCIF_D15 (MSB)

MCIF_D[14:0]

MCIF_A[9:2]

MCIF_A1

MCIF_S32

MCIF_STRB

MCIF_CS

MCIF_RW

MCIF_ACK

INT

D15 (MSB)

D[14:0]

Address Bus

Address (LSB+1)

Address LSB

CS

RW

DTACK

INT

NC

3.3 V

NOTES:

1. MCIF_S32 is used for controllers that can supply a single address for a 32-bit transaction.

2. MCIF_STRB is provided for controllers that have separate strobe and chip select signals. The MCIF_STRB

and MCIF_CS signals can be tied together if the application processor does not have a separate strobe

signal.

Figure 31. Interface Between ceLynx and 68000-Style Processor

Read Operation

3.1.1

Figure 32 depicts a typical read operation using 16-bit transactions. The host begins the read access by

driving the address to be read from onto MCIF_A[9:1]. The host then drives MCIF_RW high to indicate a

read. The host drives MCIF_STRB low to indicate that it is ready to receive the data. MCIF_CS selects the

link as the peripheral being accessed. Note the MCIF_STRB signal acts as a master enable on the

microcontroller interface. No transactions occur unless MCIF_STRB is active. The address is sampled on

the falling edge of MCIF_CS and begins the internal read access to the specified CFR. After the 16-bit word

is retrieved from the internal CFR, the link responds by driving the data onto the data bus and driving

MCIF_ACK low to indicate that data is available

The difference in functionality of a 32-bit read transaction is that the host indicates a 32-bit access by driving

MCIF_S32 active low. The host only gives one address for the entire transaction. In this mode, the MCIF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB42AA9IPZT | STORAGELYNX 1394 LINK-LAYER CONTROLLER FOR ATA/ATAPI STORAGE PRODUCTS |

| TSB42AB4I | IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

| TSB42AB4PGE | IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

| TSB43AA82A1 | 1394 integrated PHY and link layer controller(1394集成PHY和鏈路層控制器) |

| TSB81BA3I | IEEE 1394b THREE-PORT CABLE TRANSCEIVER/ARBITER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB42AA9IPZT | 功能描述:IC 1394 STORAGELYNX 100-TQFP RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TSB42AA9PZT | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB42AA9PZTR | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| TSB42AB4 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

| TSB42AB4I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。