- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385949 > TSB21LV03BI (Texas Instruments, Inc.) IEEE 1394-1995 Triple-Cable Transceiver/Arbiter(IEEE1394-1995 三電纜收發(fā)器/判優(yōu)器) PDF資料下載

參數(shù)資料

| 型號: | TSB21LV03BI |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | IEEE 1394-1995 Triple-Cable Transceiver/Arbiter(IEEE1394-1995 三電纜收發(fā)器/判優(yōu)器) |

| 中文描述: | 電機(jī)及電子學(xué)工程師聯(lián)合會1394-1995三線收發(fā)器/仲裁器(IEEE1394連接- 1995三電纜收發(fā)器/判優(yōu)器) |

| 文件頁數(shù): | 18/25頁 |

| 文件大?。?/td> | 351K |

| 代理商: | TSB21LV03BI |

TSB21LV03BI

IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER

SGLS108 – FEBRUARY 1999

18

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PRINCIPLES OF OPERATION

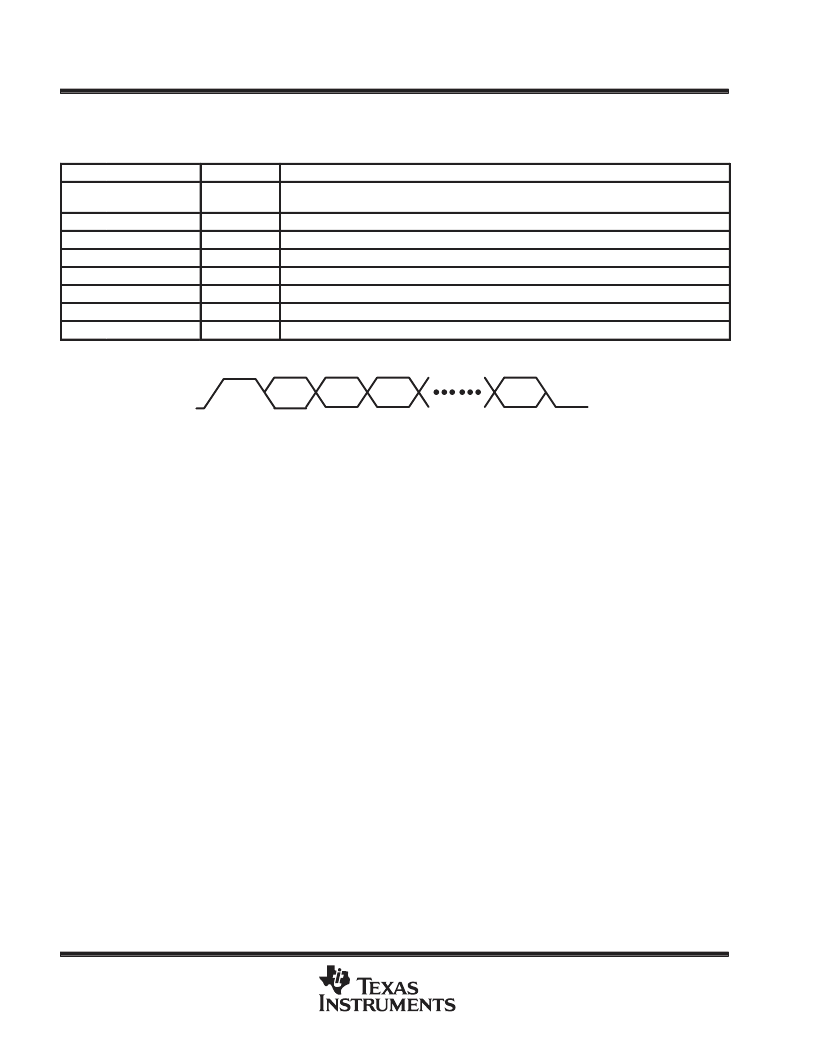

Table 9. LLC Bus Request Type

LREQ1

LREQ2

LREQ3

NAME

DESCRIPTION

0

0

0

ImmReq

Immediate request. Upon detection of an idle, the LLC takes control of the bus immediately

(no arbitration).

0

0

1

IsoReq

Isochronous request: the LLC arbitrates for the bus, no gaps.

0

1

0

PriReq

Priority request: the LLC arbitrates after a subaction gap, ignores fair protocol.

0

1

1

FairReq

Fair request: the LLC arbitrates after a subaction gap, follows fair protocol.

1

0

0

RdReg

The LLC returns the specified register contents through a status transfer.

1

0

1

WrReg

The LLC writes to the specified register.

1

1

0

Reserved

Reserved

1

1

1

Reserved

Reserved

LREQ timing (each cell represents one clock sample time):

LR0

LR1

LR2

LR3

LR(n-2)

LR(n-1)

NOTE A: Each cell represents one clock sample time.

Figure 6. LREQ Timing

For fair or priority access, the LLC requests control of the bus at least one clock after the phy-LLC interface

becomes idle. If the LLC senses that the CTLn terminals are in a receive state (CTL0 = 1, CTL1 = 0), this

indicates that its request has been lost. This is true anytime during or after the LLC sends the bus request

transfer. Additionally, the phy ignores any fair or priority requests if it asserts the receive state while the LLC is

requesting the bus. The LLC then reissues the request one clock after the next interface idle.

The cycle master uses a normal priority request to send a cycle-start message. After receiving a cycle-start

message, the LLC can issue an isochronous bus request. When arbitration is won, the LLC proceeds with the

isochronous transfer of data. The isochronous request register is cleared in the phy once the LLC sends another

type of request or when the isochronous transfer has been completed. The isochronous request must be issued

during a packet reception. Generally this request would be during reception of a cycle-start packet.

The ImmReq request is issued when the LLC needs to send an acknowledgment after reception of a packet

addressed to it. This request must be issued during packet reception. This is done to minimize the delays that

a phy would have to wait between the end of a packet and the transmittal of an acknowledgment. As soon as

the packet ends, the phy immediately grants access of the bus to the LLC. The LLC sends an acknowledgment

to the sender unless the header CRC of the packet turns out to be bad. In this case, the LLC releases the bus

immediately; it is not allowed to send another type of packet on this grant. To guarantee this, the LLC is forced

to wait 160 ns after the end of the packet is received. The phy then gains control of the bus and the

acknowledgement with the CRC error is sent. Then the bus is released and allowed to proceed with another

request.

Although highly improbable, it is conceivable that two separate nodes can believe that an incoming packet is

intended for them. The nodes then issue an ImmReq request before checking the CRC of the packet. Since both

phys seize control of the bus at the same time, a temporary, localized collision of the bus occurs somewhere

between the competing nodes. This collision would be interpreted by the other nodes on the network as being

a high-impedance line state, not a bus reset. As soon as the two nodes check the CRC, the mistaken node drops

its request and the false line state is removed. The only side effect would be the loss of the intended

acknowledgment packet (this is handled by the higher-layer protocol).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB42AA4I | IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

| TSB42AA4PDT | IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

| TSB42AA4PGE | IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

| TSB42AA9I | STORAGELYNX 1394 LINK-LAYER CONTROLLER FOR ATA/ATAPI STORAGE PRODUCTS |

| TSB42AA9IPZT | STORAGELYNX 1394 LINK-LAYER CONTROLLER FOR ATA/ATAPI STORAGE PRODUCTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB21LV03C | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB21LV03CHV | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB21LV03CMHV | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB21LV03CMHVB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB21LV03CPM | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。