- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371186 > TLIU04C1 TLIU04C1 Quad T1/E1 Line Interface PDF資料下載

參數(shù)資料

| 型號: | TLIU04C1 |

| 英文描述: | TLIU04C1 Quad T1/E1 Line Interface |

| 中文描述: | TLIU04C1四T1/E1線路接口 |

| 文件頁數(shù): | 45/100頁 |

| 文件大小: | 1321K |

| 代理商: | TLIU04C1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

Advance Data Sheet, Rev. 2

April 1999

TLIU04C1 Quad T1/E1 Line Interface

45

Lucent Technologies Inc.

Microprocessor Mode

(continued)

Registers

(continued)

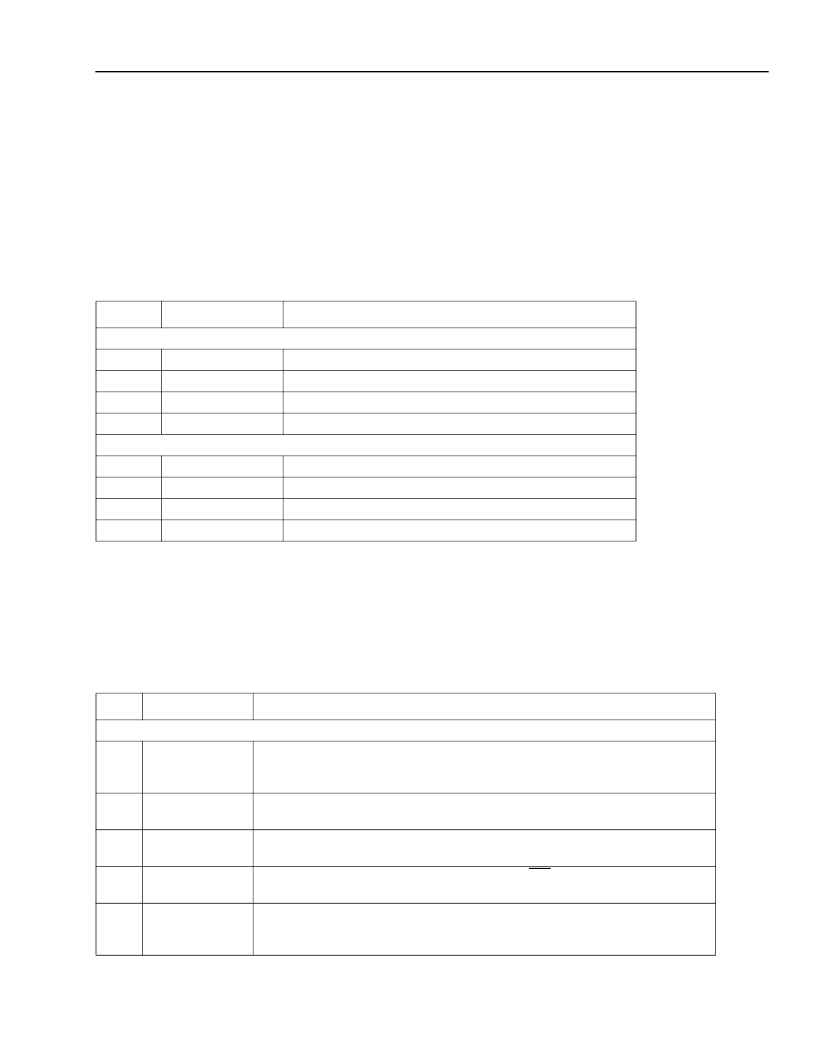

Alarm Mask Registers (0010, 0011)

The bits in the alarm mask registers in Table 22 allow the microprocessor to selectively mask each channel alarm

and prevent it from generating an interrupt. The mask bits correspond to the alarm status bits in the alarm registers

and are active-high to disable the corresponding alarm from generating an interrupt. These registers are read/write

registers.

*The numerical suffix identifies the channel number.

Global Control Registers (0100, 0101)

The bits in the global control registers in Table 23 and Table 24 allow the microprocessor to configure the various

device functions over all the four channels. All the control bits (with the exception of LOSSTD and ICTMODE) are

active-high. These are read/write registers.

Table 22. Alarm Mask Registers

Bits

Symbol

*

Description

Alarm Mask Register (2)

Mask analog loss of signal alarm for channels 1 and 2.

Mask digital loss of signal alarm for channels 1 and 2.

Mask transmit driver monitor alarm for channels 1 and 2.

Mask loss of transmit clock alarm for channels 1 and 2.

Alarm Mask Register (3)

Mask analog loss of signal alarm for channels 3 and 4.

Mask digital loss of signal alarm for channels 3 and 4.

Mask transmit driver monitor alarm for channels 3 and 4.

Mask loss of transmit clock alarm for channels 3 and 4.

0, 4

1, 5

2, 6

3, 7

MALOS[1—2]

MDLOS[1—2]

MTDM[1—2]

MLOTC[1—2]

0, 4

1, 5

2, 6

3, 7

MALOS[3—4]

MDLOS[3—4]

MTDM[3—4]

MLOTC[3—4]

Table 23. Global Control Register (0100)

Bits

Symbol

Description

Global Control Register (4)

The GMASK bit globally masks all the channel alarms when GMASK = 1, pre-

venting all the receiver and transmitter alarms from generating an interrupt.

GMASK = 1 after a device reset.

The SWRESET provides the same function as the hardware reset. It is used

for device initialization through the microprocessor interface.

The LOSSTD bit selects the conformance protocol for the DLOS receiver

alarm function.

The ICTMODE bit changes the function of the ICT pin. ICTMODE = 0 after a

device reset.

A HIGHZ bit is available for each individual channel. When HIGHZ = 1, the

TTIP and TRING transmit drivers for the specified channel are placed in a

high-impedance state. HIGHZ [1—4] = 1 after a device reset.

0

GMASK

1

SWRESET

2

LOSSTD

3

ICTMODE

4—7

HIGHZ[1—4]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLIU04C1 | Quad T1/E1 Line Interface(四T1/E1線接口) |

| TLV3011AIDBVR | Nanopower, 1.8V, SOT23 Comparator with Voltage Reference |

| TLV349x | CAPACITOR, CLASS Y2 1.0NFCAPACITOR, CLASS Y2 1.0NF; Capacitance:1nF; Voltage rating, AC:250V; Voltage rating, DC:2500V; Capacitor dielectric type:Polypropylene; Series:B81122; Tolerance, +:20%; Tolerance, -:20%; Temp, op. |

| TLV3011AIDBVT | Nanopower, 1.8V, SOT23 Comparator with Voltage Reference |

| TLV3011AIDCKR | Nanopower, 1.8V, SOT23 Comparator with Voltage Reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLIXF30001 | 制造商:GIGA 功能描述: |

| TLIXF30003 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TLIXF30007-852838 | 制造商:Cortina Systems Inc 功能描述: |

| TLIXF30009-865852 | 功能描述:IC OPT TRANSPORT PROC 868-TBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 電信 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS 產(chǎn)品變化通告:Product Discontinuation 06/Feb/2012 標(biāo)準(zhǔn)包裝:750 系列:* |

| TLIXF30010 | 制造商:Intel 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。