- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378162 > RM7065A (PMC-SIERRA INC) 64-Bit MIPS RISC Microprocessor with Integrated L2 Cache PDF資料下載

參數(shù)資料

| 型號: | RM7065A |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-Bit MIPS RISC Microprocessor with Integrated L2 Cache |

| 中文描述: | 64-BIT, 400 MHz, RISC PROCESSOR, PBGA256 |

| 封裝: | 27 X 27 MM, TBGA-256 |

| 文件頁數(shù): | 26/52頁 |

| 文件大小: | 776K |

| 代理商: | RM7065A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer

’

s Internal Use

Document ID: PMC-2010145, Issue 2

26

RM7065A

Microprocessor with On-Chip Secondary Cache Data Sheet

Preliminary

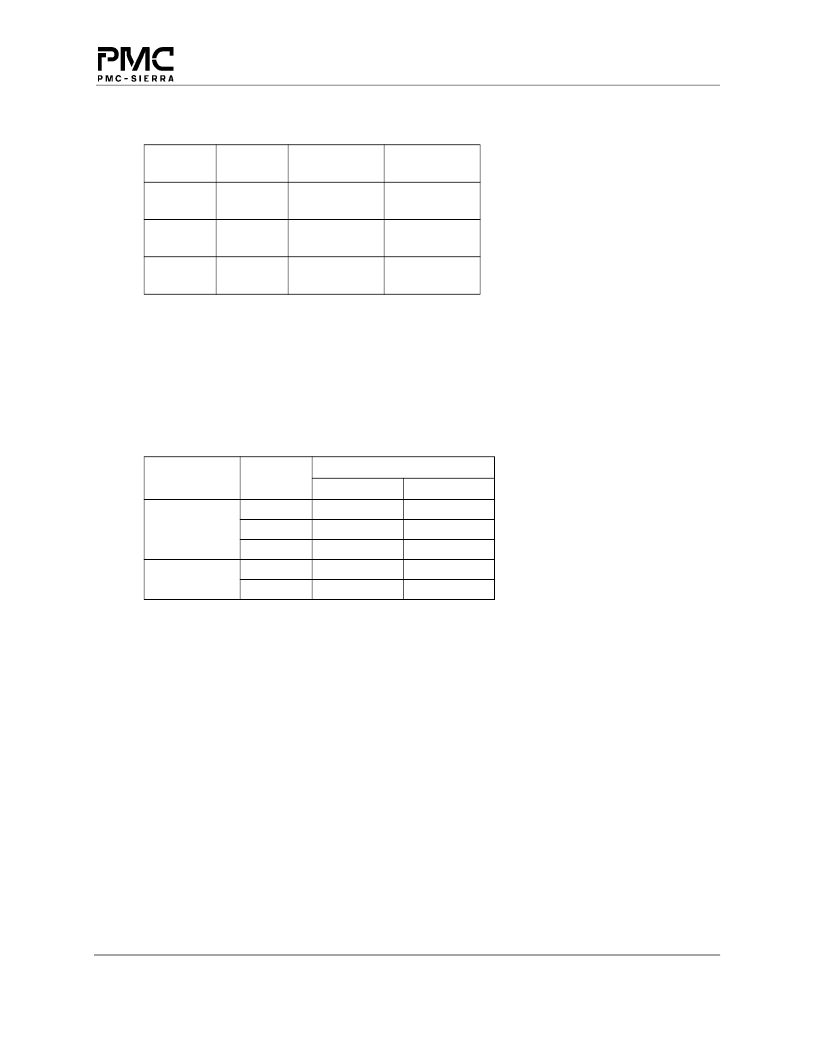

Table 7 Cache Locking Control

Lock

Enable

Primary I

ECC[27]

4.22 Cache Management

To improve the performance of critical data movement operations in the embedded environment,

the RM7065A significantly improves the speed of operation of certain critical cache management

operations. In particular, the speed of the Hit-Writeback-Invalidate and Hit-Invalidate cache

operations has been improved, in some cases by an order of magnitude, over that of other MIPS

processors. For example, Table 8 compares the RM7065A with the R4000 processor.

Table 8 Penalty Cycles

For the Hit-Dirty case of Hit-Writeback-Invalidate in Table 8 above, if the writeback buffer is full

from some previous cache eviction, then n is the number of cycles required to empty the writeback

buffer. If the buffer is empty then n is zero.

The penalty value in Table 8 is the number of processor cycles beyond the one cycle required to

issue the instruction that is required to implement the operation.

4.23 Primary Write Buffer

Writes to secondary cache or external memory, whether cache miss write-backs or stores to

uncached or write-through addresses, use the integrated primary write buffer. The write buffer

holds up to four 64-bit address and data pairs. The entire buffer is used for a data cache write-back

and allows the processor to proceed in parallel with memory update. For uncached and write-

through stores, the write buffer significantly increases performance by decoupling the

SysAD

bus

transfers from the instruction execution stream.

4.24 System Interface

The RM7065A provides a high-performance 64-bit system interface which is compatible with the

RM5200 Family. As an enhancement to the

SysAD

bus interface, the RM7065A allows half-

Cache

Set Select

ECC[28]=0

→

A

ECC[28]=1

→

B

ECC[28]=0

→

A

ECC[28]=1

→

B

ECC[28]=0

→

A

ECC[28]=1

→

B

Activate

Fill_I

Primary D

ECC[26]

Load/Store

Secondary

ECC[25]

Fill_I or

Load/Store

Operation

Hit-Writeback-

Invalidate

Condition

Miss

Hit-Clean

Hit-Dirty

Miss

Hit

Penalty

RM7065A

R4000

0

3

7

12

3+n

0

2

14+n

7

9

Hit-Invalidate

相關PDF資料 |

PDF描述 |

|---|---|

| RM7065A-300T | RM7065A⑩ Microprocessor with On-Chip Secondary Cache Data Sheet Preliminary |

| RM7065A-350T | RM7065A⑩ Microprocessor with On-Chip Secondary Cache Data Sheet Preliminary |

| RM805 | LEAD FREE 8-BIT 50V SER-IN LATCHED DRV |

| RM805-17 | LEAD FREE A6841 SOIC-20 |

| RMDA1840 | 18-40 GHz Broad Band Driver Amplifier MMIC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| RM7065A-300R-D002 | 制造商:PMC Sierra from Components Direct 功能描述:RM7065A-300R-D002 - Trays 制造商:PMC-Sierra 功能描述:PMC-Sierra RM7065A-300R-D002 Microprocessors |

| RM7065C-466L-D004 | 制造商:PMC Sierra from Components Direct 功能描述:RM7065C-466L-D004 - Trays 制造商:PMC-Sierra 功能描述:PMC-Sierra RM7065C-466L-D004 Microprocessors |

| RM7065C-600T-D004 | 制造商:PMC-Sierra 功能描述: |

| RM707012 | 功能描述:通用繼電器 3PDT 16A 12VDC 86Ohm POWER RELAY RoHS:否 制造商:Omron Electronics 觸點形式:1 Form A (SPST-NO) 觸點電流額定值:150 A 線圈電壓:24 VDC 線圈電阻:144 Ohms 線圈電流:167 mA 切換電壓:400 V 安裝風格:Chassis 觸點材料: |

| RM707024 | 功能描述:通用繼電器 16 AMP 24VDC 3PDT RoHS:否 制造商:Omron Electronics 觸點形式:1 Form A (SPST-NO) 觸點電流額定值:150 A 線圈電壓:24 VDC 線圈電阻:144 Ohms 線圈電流:167 mA 切換電壓:400 V 安裝風格:Chassis 觸點材料: |

發(fā)布緊急采購,3分鐘左右您將得到回復。