- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378162 > RM5231A-250-H (PMC-SIERRA INC) RM5231A⑩ Microprocessor with 32-Bit System Bus Data Sheet Preliminary PDF資料下載

參數(shù)資料

| 型號(hào): | RM5231A-250-H |

| 廠商: | PMC-SIERRA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RM5231A⑩ Microprocessor with 32-Bit System Bus Data Sheet Preliminary |

| 中文描述: | 64-BIT, 250 MHz, MICROPROCESSOR, PQFP128 |

| 封裝: | MQFP-128 |

| 文件頁(yè)數(shù): | 13/40頁(yè) |

| 文件大小: | 595K |

| 代理商: | RM5231A-250-H |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

Document ID: PMC-2002174, Issue 2

13

RM5231A Microprocessor with 32-Bit System Bus Data Sheet

Preliminary

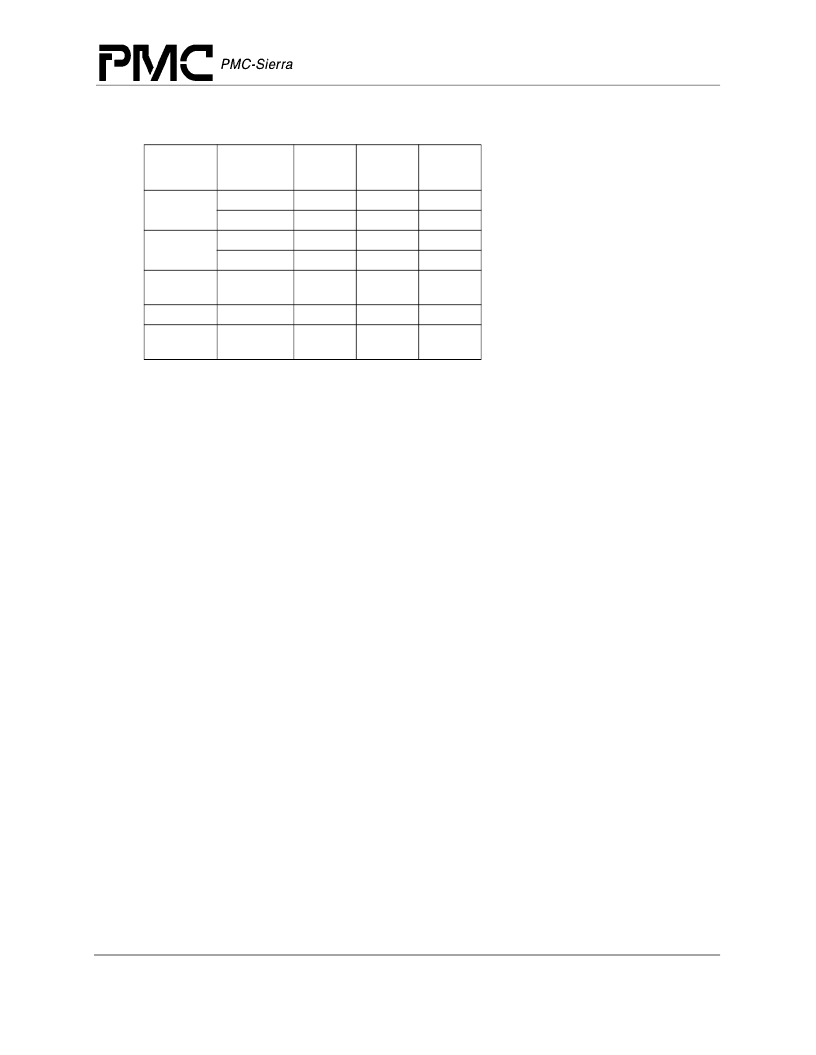

Table 1 Integer Multiply/Divide Operations

The baseline MIPS IV ISA specifies that the results of a multiply or divide operation be placed in

the

Hi

and

Lo

registers. These values can then be transferred to the general purpose register file

using the Move-from-Hi and Move-from-Lo (

MFHI

/

MFLO

) instructions.

In addition to the baseline MIPS IV integer multiply instructions, the RM5231A also implements

the 3 operand multiply instruction,

MUL

. This instruction specifies that the multiply result go

directly to the integer register file rather than the Lo register. The portion of the multiply that

would have normally gone into the Hi register is discarded. For applications where it is known that

the upper half of the multiply result is not required, using the

MUL

instruction eliminates the

necessity of executing an explicit

MFLO

instruction.

Also included in the RM5231A are the multiply-add instructions,

MADU

/

MAD

. This instruction

multiplies two operands and adds the resulting product to the current contents of the Hi and Lo

registers. The multiply-accumulate operation is the core primitive of almost all signal processing

algorithms allowing the RM5231A to eliminate the need for a separate DSP engine in many

embedded applications.

Floating-Point Co-Processor

3.8

The RM5231A incorporates a high-performance fully pipelined floating-point co-processor which

includes a floating-point register file and autonomous execution units for multiply/add/convert and

divide/square root. The floating-point coprocessor is a tightly coupled execution unit, decoding

and executing instructions in parallel with, and in the case of floating-point loads and stores, in

cooperation with the integer unit. The superscalar capabilities of the RM5231A allow floating-

point computation instructions to issue concurrently with integer instructions.

Floating-Point Unit

3.9

The RM5231A floating-point execution unit supports single and double precision arithmetic, as

specified in the IEEE Standard 754. The execution unit is broken into a separate divide/square root

unit and a pipelined multiply/add unit. Overlap of the divide/square root and multiply/add

operations is supported.

The RM5231A maintains fully precise floating-point exceptions while allowing both overlapped

and pipelined operations. Precise exceptions are extremely important in object-oriented

programming environments and highly desirable for debugging in any environment.

Opcode

MULT/U,

MAD/U

Operand

Size

16 bit

32 bit

16 bit

32 bit

any

Latency

3

4

3

4

7

Repeat

Rate

2

3

2

3

6

Stall

Cycles

0

0

1

2

0

MUL

DMULT,

DMULTU

DIV, DIVD

DDIV,

DDIVU

any

any

36

68

36

68

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RM5231A-300-H | RM5231A⑩ Microprocessor with 32-Bit System Bus Data Sheet Preliminary |

| RM5231A-300-HI | RM5231A⑩ Microprocessor with 32-Bit System Bus Data Sheet Preliminary |

| RM5231A-350-H | RM5231A⑩ Microprocessor with 32-Bit System Bus Data Sheet Preliminary |

| RM5261A | RM5261A⑩ Microprocessor with 64-Bit System Bus Data Sheet Preliminary |

| RM5261A-250-H | RM5261A⑩ Microprocessor with 64-Bit System Bus Data Sheet Preliminary |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RM525A-R2 | 制造商:Black Box Corporation 功能描述:2U Wallmount Cabinet, Beige |

| RM5260-133Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5260-150Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5260-175Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

| RM5260-200Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Microprocessor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。