- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359235 > MT9196AE1 (ZARLINK SEMICONDUCTOR INC) Integrated Digital Phone Circuit (IDPC) PDF資料下載

參數(shù)資料

| 型號(hào): | MT9196AE1 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類(lèi): | 通信及網(wǎng)絡(luò) |

| 英文描述: | Integrated Digital Phone Circuit (IDPC) |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PDIP28 |

| 封裝: | 0.600 INCH, LEAD FREE, PLASTIC, MS-011AB, DIP-28 |

| 文件頁(yè)數(shù): | 14/46頁(yè) |

| 文件大小: | 631K |

| 代理商: | MT9196AE1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

MT9196

Data Sheet

14

Zarlink Semiconductor Inc.

The D-Channel read register is not preset to any particular value on power-up (PWRST) or software reset (RST).

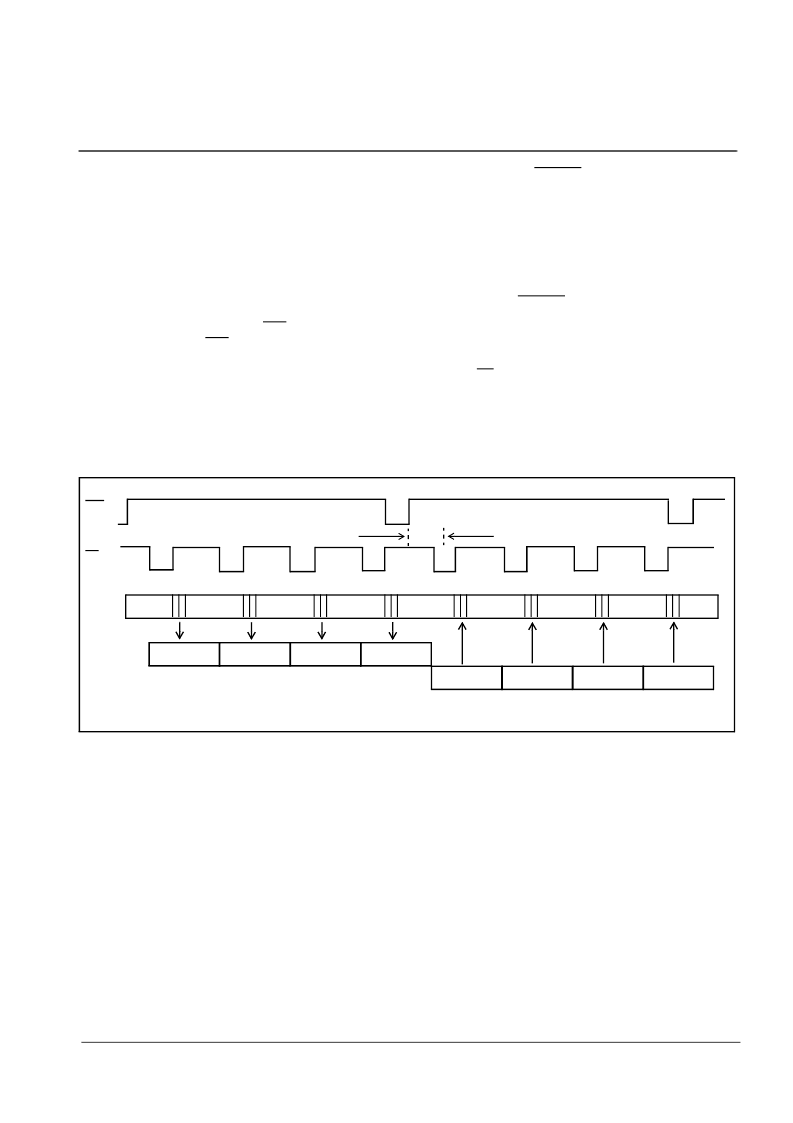

b. A microport write to Address 15hex will result in a byte of data being loaded which is composed of four di-

bits (designated by roman numerals I, II, III, IV). These di-bits are destined for the two D-Channel bits

transmitted during each of frames n+1, n+2, n+3, n+4. Referring to Fig.8a: di-bit I is mapped to frame

n+1, di-bit II is mapped to frame n+2, di bit III is mapped to frame n+3 and di bit IV is mapped to frame

n+4.

If no new data is written to address 15hex, the current D-channel register contents will be continuously re-

transmitted. The D-Channel write register is preset to all ones on power-up (PWRST) or software reset (RST).

An interrupt output is provided (IRQ) to synchronize microprocessor access to the D-Channel register during valid

ST-BUS periods only. IRQ will occur every fourth (eighth in 8 kb/s mode) ST-BUS frame at the beginning of the third

(second in 8 kb/s mode) ST-BUS bit cell period. The interrupt will be removed following a microprocessor Read or

Write of Address 15 hex or upon encountering the following frames’s FP input, whichever occurs first. To ensure D-

Channel data integrity, microport read/write access to Address 15 hex must occur before the following frame pulse.

See Figure 8b for timing.

8 kb/s operation expands the interrupt to every eight frames and processes data one-bit-per-frame. D-Channel

register data is mapped according to Figure 8c.

Figure 8a - D-Channel 16 kb/s Operation

n-3

n-2

n-1

n

n+1

n+2

n+3

n+4*

Microport Read/Write Access

D0

D1

I

D2

D3

II

D4

D5

III

D6

Di-bit Group

Transmit

D-Channel

D7

IV

D0

D1

I

D2

Power-up reset to 1111 1111

D3

II

D4

D5

III

D6

D7

IV

No preset value

* note that frame n+4 is equivalent to frame n of the next cycle.

IRQ

FP

DSTo/

DSTi

Di-bit Group

Receive

D-Channel

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT92220 | 1023 Channel Voice Over IP/AAL2 Processor |

| MT9300B | Multi-Channel Voice Echo Canceller |

| MT9300BL | Multi-Channel Voice Echo Canceller |

| MT9300BV | Multi-Channel Voice Echo Canceller |

| MT9315 | CMOS Acoustic Echo Canceller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9196AP | 制造商:Microsemi Corporation 功能描述: |

| MT9196AP1 | 制造商:Microsemi Corporation 功能描述:INTEGRATED DGTL PHONE CIRCUIT (IDPC) 28PLCC - Rail/Tube 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC DGTL TELEPHONE CIRCUIT 28PLCC 制造商:Microsemi Corporation 功能描述:IC DGTL TELEPHONE CIRCUIT 28PLCC |

| MT9196APR | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Integrated Digital Phone Circuit (IDPC) |

| MT9196APR1 | 制造商:Microsemi Corporation 功能描述:INTEGRATED DGTL PHONE CIRCUIT (IDPC) 28PLCC - Tape and Reel 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC DGTL TELEPHONE CIRCUIT 28PLCC 制造商:Microsemi Corporation 功能描述:IC DGTL TELEPHONE CIRCUIT 28PLCC |

| MT9196AS | 制造商:Microsemi Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。