- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378678 > MSM5416263 (OKI SEMICONDUCTOR CO., LTD.) 262,144-Word ×16-Bit Multiport DRAM(256k字×16位多端口動態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號: | MSM5416263 |

| 廠商: | OKI SEMICONDUCTOR CO., LTD. |

| 英文描述: | 262,144-Word ×16-Bit Multiport DRAM(256k字×16位多端口動態(tài)RAM) |

| 中文描述: | 262,144字× 16位多端口內(nèi)存(256k字× 16位多端口動態(tài)RAM)的 |

| 文件頁數(shù): | 39/40頁 |

| 文件大小: | 389K |

| 代理商: | MSM5416263 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁

Semiconductor

MSM5416263

39/40

SAM Stop Set Cycle (CBRS):

RAS

falling edge ---

CAS

= "L",

WEL

or

WEU

= "L", DSF = "H"

SAM stop location data (boundaries) are latched from address inputs at the falling edge of

RAS

.

To determine the boundary A4 - A7 are used, and A0 - A3, and A8 are ignored.

Once the CBRS is executed, the programmable SAM stop operation continues until CBRR.

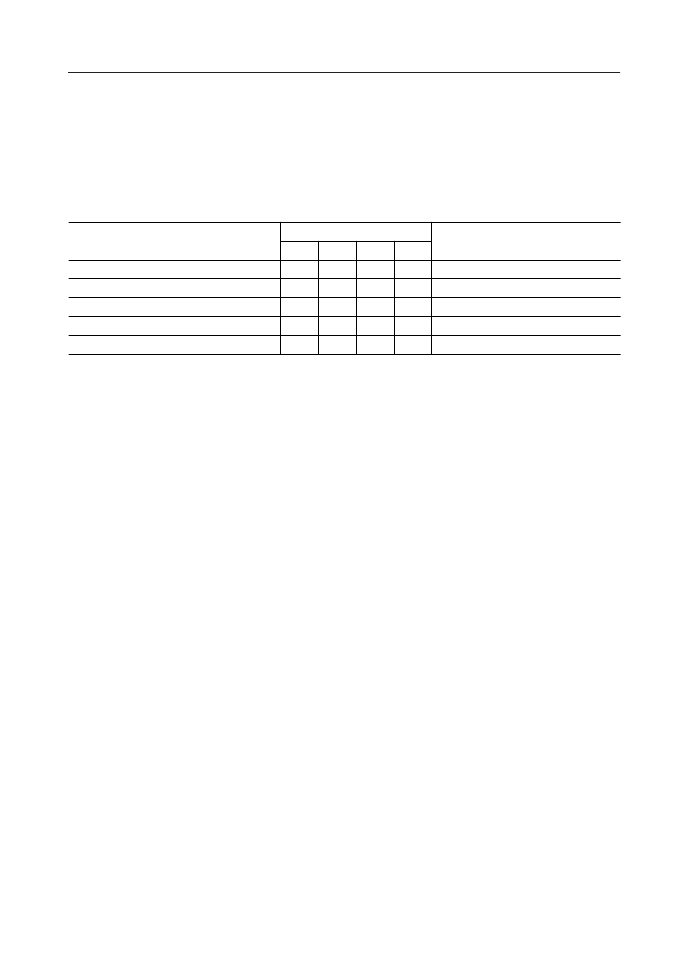

SAM Stop Boundary Table

Number of Stop Points

1

2

4

8

16

Address

A5

1

1

1

0

X

A4

1

1

1

1

0

A6

1

1

0

X

X

A7

1

0

X

X

X

256

128

64

32

16

Size of Partition

Register Reset Cycle (CBRR):

RAS

falling edge ---

CAS

= "L",

WEL

=

WEU

= "H", DSF = "L"

A CBRR can reset the programmable SAM stop operation, and persistent mask write operation.

The CBRR will take effect immediately; it doesn’t require a split transfer cycle.

POWER UP

Power must be applied to the

RAS

and

TRG

input signals to pull them "high" before, or at the

same time as, the V

CC

supply is turned on. After power-up, a pause of 200

m

s minimum is

required with

RAS

and

TRG

held "high". After the pause, a minimum of 8

RAS

and 8 SC dummy

cycles must be performed to stabilize the internal circuitry, before valid read, write or transfer

operations can begin. During the initialization period, the

TRG

signal must be held "high". If the

internal refresh counter is used, a minimum 8

CAS

before

RAS

cycles are required instead of 8

RAS

cycles.

(NOTE) INITIAL STATE AFTER POWER UP

The initial state can not be guaranteed for various power up conditions and input signal levels.

Therefore, it is recommended that the initial state be set (ex. Perform a CBRR cycle to select Non

Persistent Write-per-bit mode) after the initialization of the device is performed and before valid

operations begin.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM548128BL | 131,072-Word ×8-Bit High-Speed PSRAM(128k字×8位高速偽靜態(tài)RAM) |

| MSM548332 | 278,400-Word×12-Bit Field Memory(278,400字×12位場存儲器) |

| MSM54V32126A | 131,072-Word X 32-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO |

| MSM54V32126A-45GS-K | 131,072-Word X 32-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO |

| MSM54V32126A-45TS-K | 131,072-Word X 32-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM5416263-60G3-K | 制造商:ROHM Semiconductor 功能描述: |

| MSM5416263-60GS-K | 制造商:ROHM Semiconductor 功能描述: |

| MSM5416273-50G3-K | 制造商:ROHM Semiconductor 功能描述:DUE TO FLOOD DAMAGE TO TESTERS |

| MSM5416273-50GS-K | 制造商:ROHM Semiconductor 功能描述: 制造商:OK International 功能描述:256K X 16 VIDEO DRAM, 50 ns, PDSO64 |

| MSM541627360GSK | 制造商:OK International 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。