- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45285 > MC9328MX21DVG (FREESCALE SEMICONDUCTOR INC) 266 MHz, MICROPROCESSOR, PBGA289 PDF資料下載

參數(shù)資料

| 型號(hào): | MC9328MX21DVG |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 266 MHz, MICROPROCESSOR, PBGA289 |

| 封裝: | 14 X 14 MM, 1.41 MM HEIGHT, 0.65 MM PITCH, MAPBGA-289 |

| 文件頁(yè)數(shù): | 21/106頁(yè) |

| 文件大小: | 1932K |

| 代理商: | MC9328MX21DVG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)

Specifications

MC9328MX21 Product Preview, Rev. 1.1

Freescale Semiconductor

21

3.7

External DMA Request and Grant

The External DMA request is an active low signal to be used by devices external to i.MX21 processor to request

the DMAC for data transfer.

After assertion of External DMA request the DMA burst will start when the channel on which the External request

is the source (as per the RSSR settings) becomes the current highest priority channel. The external device using the

External DMA request should keep its request asserted until it is serviced by the DMAC. One External DMA

request will initiate one DMA burst.

The output External Grant signal from the DMAC is an active-low signal.When the following conditions are true,

the External DMA Grant signal is asserted with the initiation of the DMA burst.

The DMA channel for which the DMA burst is ongoing has request source as external DMA Request (as

per source select register setting).

REN and CEN bit of this channel are set.

External DMA Request is asserted.

After the grant is asserted, the External DMA request will not be sampled until completion of the DMA burst. As

the external request is synchronized, the request synchronization will not be done during this period. The priority of

the external request becomes low for the next consecutive burst, if another DMA request signal is asserted.

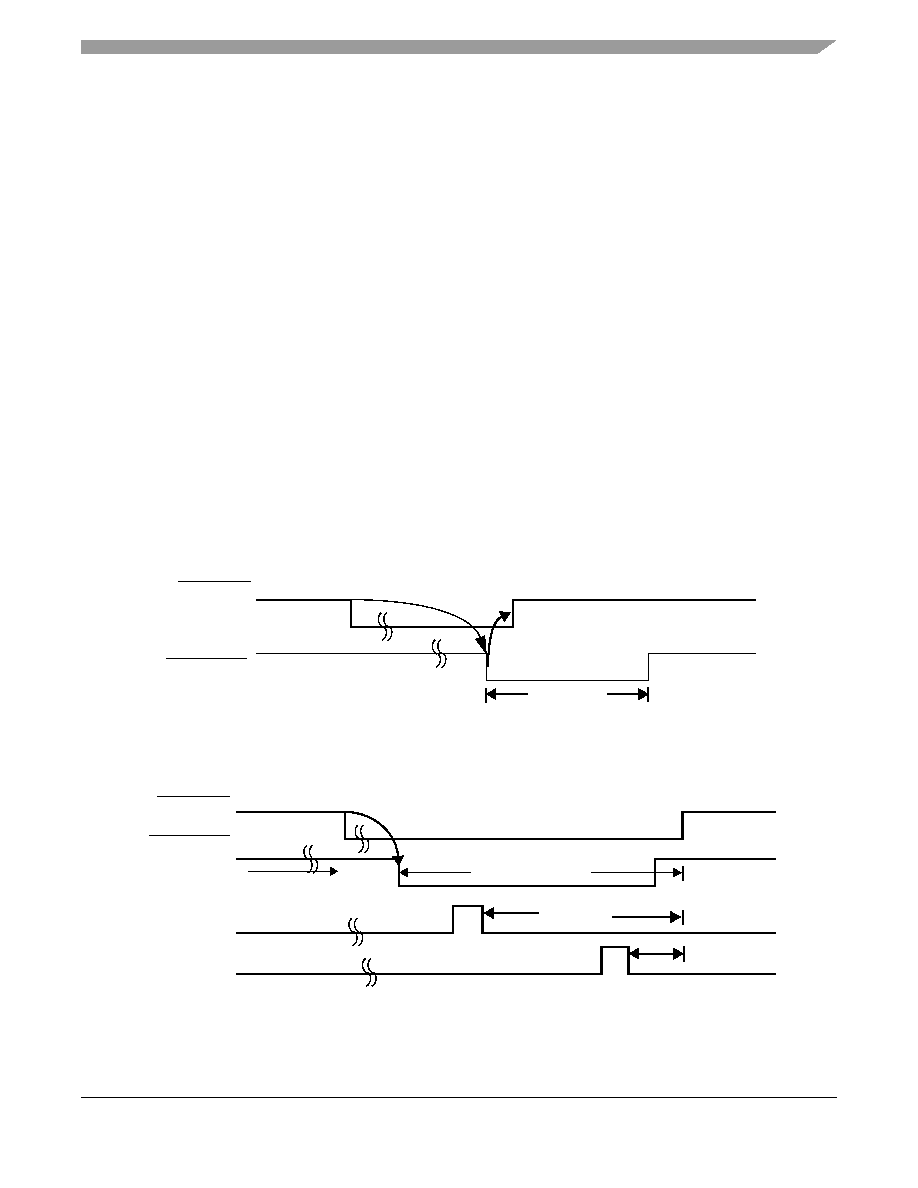

Worst case—that is, the smallest burst (1 byte read/write) timing diagrams are shown in Figure 4 and Figure 5 on

page 21. Minimum and maximum timings for the External request and External grant signals are present in

Figure 4 shows the minimum time for which the External Grant signal remains asserted when an External DMA

request is de-asserted immediately after sensing grant signal active.

Figure 4. Assertion of DMA External Grant Signal

Figure 5 shows the safe maximum time for which External DMA request can be kept asserted, after sensing grant

signal active such that a new burst is not initiated.

Figure 5. Safe Maximum Timings for External Request De-Assertion

Ext_DMAReq

Ext_DMAGrant

tmin_assert

Ext_DMAReq

Data read from

External device

Data written to

External device

Ext_DMAGrant

tmax_write

tmax_read

tmax_req_assert

NOTE: Assuming in worst case the data is read/written from/to External device as per the above waveform.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC9328MXLCVM15R2 | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA256 |

| MC9328MXLDVM15 | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA256 |

| MC9328MXLCVM15 | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA256 |

| MC9328MXLDVP15R2 | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA225 |

| MC9328MXLVP15R2 | 32-BIT, 150 MHz, RISC PROCESSOR, PBGA225 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC9328MX21DVGR2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC9328MX21DVH | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:i.MX family of microprocessors |

| MC9328MX21DVK | 功能描述:處理器 - 專門應(yīng)用 DB I.MX21 PB-FR RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MC9328MX21DVK | 制造商:Freescale Semiconductor 功能描述:Microprocessor |

| MC9328MX21DVKR2 | 功能描述:處理器 - 專門應(yīng)用 DB I.MX21 PB-FR RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。