- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45249 > MC7447RX1267LB (MOTOROLA INC) 32-BIT, 1267 MHz, RISC PROCESSOR, CBGA360 PDF資料下載

參數(shù)資料

| 型號: | MC7447RX1267LB |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 1267 MHz, RISC PROCESSOR, CBGA360 |

| 封裝: | 25 X 25 MM, 3.20 MM HEIGHT, 1.27 MM PITCH, CERAMIC, FLIP CHIP, BGA-360 |

| 文件頁數(shù): | 13/87頁 |

| 文件大?。?/td> | 1586K |

| 代理商: | MC7447RX1267LB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁

20

MPC7457 RISC Microprocessor Hardware Specifications

MOTOROLA

Electrical and Thermal Characteristics

1.5.2.3

L3 Clock AC Specifications

The L3_CLK frequency is programmed by the L3 configuration register core-to-L3 divisor ratio. See

Table 18 for example core and L3 frequencies at various divisors. Table 10 provides the potential range of

L3_CLK output AC timing specifications as defined in Figure 7.

The maximum L3_CLK frequency is the core frequency divided by two. Given the high core frequencies

available in the MPC7457, however, most SRAM designs will be not be able to operate in this mode using

current technology and, as a result, will select a greater core-to-L3 divisor to provide a longer L3_CLK

period for read and write access to the L3 SRAMs. Therefore, the typical L3_CLK frequency shown in

Table 10 is considered to be the practical maximum in a typical system. The maximum L3_CLK frequency

for any application of the MPC7457 will be a function of the AC timings of the MPC7457, the AC timings

for the SRAM, bus loading, and printed-circuit board trace length, and may be greater or less than the value

given in Table 10. Note that SYSCLK input jitter and L3_CLK[0:1] output jitter are already comprehended

in the L3 bus AC timing specifications and do not need to be separately accounted for in an L3 AC timing

analysis. Clock skews, where applicable, do need to be accounted for in an AC timing analysis.

Motorola is similarly limited by system constraints and cannot perform tests of the L3 interface on a

socketed part on a functional tester at the maximum frequencies of Table 10. Therefore, functional operation

and AC timing information are tested at core-to-L3 divisors which result in L3 frequencies at 250 MHz or

lower.

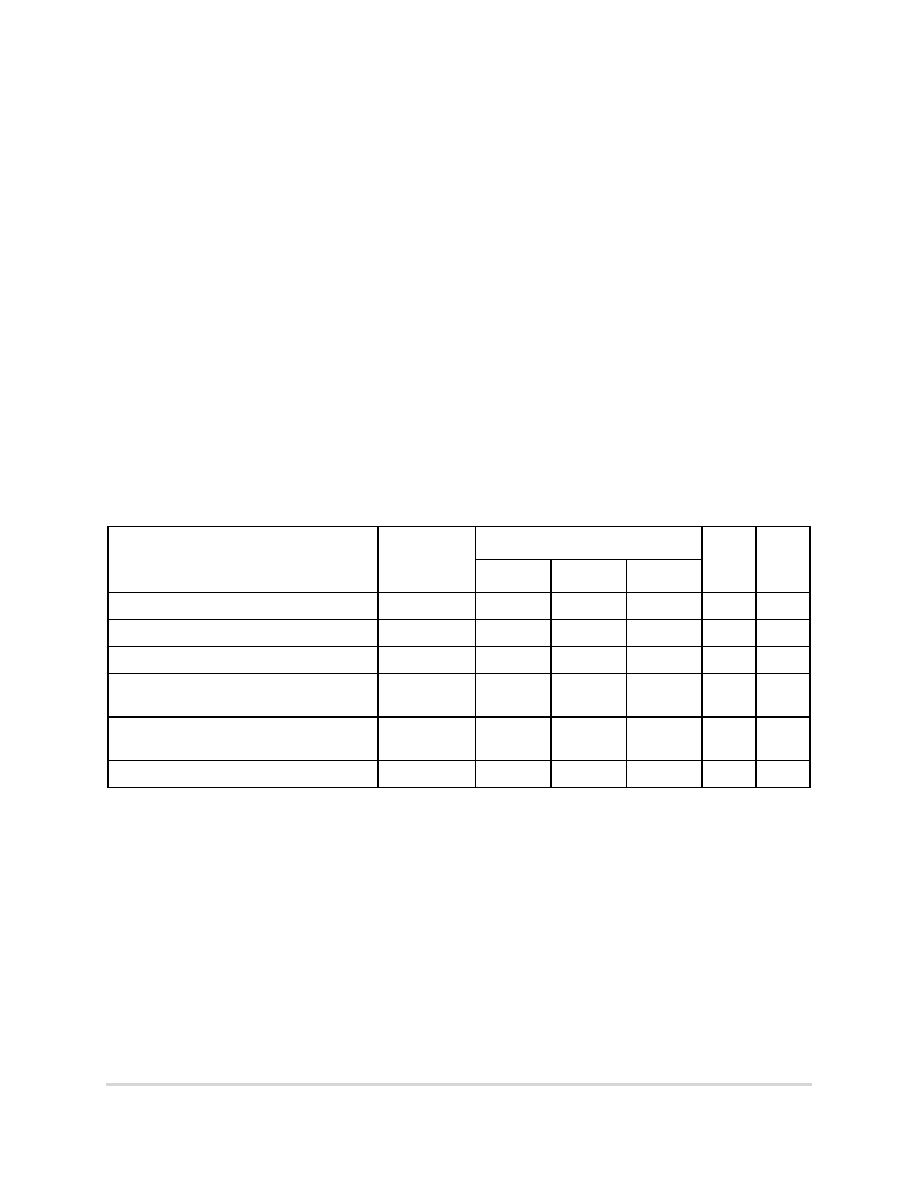

Table 10. L3_CLK Output AC Timing Specifications

At recommended operating conditions. See Table 4.

Parameter

Symbol

All Speed Grades

Unit

Notes

Minimum

Typical

Maximum

L3 clock frequency

fL3_CLK

—

200

—

MHz

1

L3 clock cycle time

tL3_CLK

—5.0

—

ns

1

L3 clock duty cycle

tCHCL/tL3_CLK

—50

—

%

2

L3 clock output-to-output skew (L3_CLK0 to

L3_CLK1)

tL3CSKW1

—

100

ps

3

L3 clock output-to-output skew

(L3_CLK[0:1] to L3_ECHO_CLK[1,3])

tL3CSKW2

—

100

ps

4

L3 clock jitter

—

± 75

ps

5

Notes:

1. The maximum L3 clock frequency (and minimum L3 clock period) will be system dependent. See Section 1.5.2.3,

“L3 Clock AC Specifications,” for an explanation that this maximum frequency is not functionally tested at speed by

Motorola. The minimum L3 clock frequency and period are fSYSCLK and tSYSCLK, respectively.

2. The nominal duty cycle of the L3 output clocks is 50% measured at midpoint voltage.

3. Maximum possible skew between L3_CLK0 and L3_CLK1. This parameter is critical to the address and control

signals which are common to both SRAM chips in the L3.

4. Maximum possible skew between L3_CLK0 and L3_ECHO_CLK1 or between L3_CLK1 and L3_ECHO_CLK3 for

PB2 or Late Write SRAM. This parameter is critical to the read data signals because the processor uses the

feedback loop to latch data driven from the SRAM, each of which drives data based on L3_CLK0 or L3_CLK1.

5. Guaranteed by design and not tested. The input jitter on SYSCLK affects L3 output clocks and the L3 address, data,

and control signals equally and, therefore, is already comprehended in the AC timing and does not have to be

considered in the L3 timing analysis. The clock-to-clock jitter shown here is uncertainty in the internal clock period

caused by supply voltage noise or thermal effects. This is also comprehended in the AC timing specifications and

need not be considered in the L3 timing analysis.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC7447RX1200LB | 32-BIT, 1200 MHz, RISC PROCESSOR, CBGA360 |

| MC7457VG1200LC | 32-BIT, 1200 MHz, RISC PROCESSOR, CBGA483 |

| MC7447RX867LB | 32-BIT, 867 MHz, RISC PROCESSOR, CBGA360 |

| MC7448VS1267NC | 32-BIT, 1267 MHz, RISC PROCESSOR, CBGA360 |

| MC7448VU1400NC | 32-BIT, 1400 MHz, RISC PROCESSOR, CBGA360 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC7447RX600NB | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:PPC7457RX1000NB |

| MC7447RX733NB | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

| MC7447RX867NB | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:PPC7457RX1000NB |

| MC7448HX1000LC | 功能描述:IC MPU RISC 32BIT 360-FCCBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:MPC74xx 標(biāo)準(zhǔn)包裝:1 系列:MPC85xx 處理器類型:32-位 MPC85xx PowerQUICC III 特點:- 速度:1.2GHz 電壓:1.1V 安裝類型:表面貼裝 封裝/外殼:783-BBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:783-FCPBGA(29x29) 包裝:托盤 |

| MC7448HX1000LD | 功能描述:微處理器 - MPU APL8 RV2.2.1 1.15V 105C RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。