- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄69026 > MC68HC05JB3JDW (MOTOROLA INC) 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | MC68HC05JB3JDW |

| 廠商: | MOTOROLA INC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PDSO28 |

| 封裝: | SOIC-28 |

| 文件頁(yè)數(shù): | 85/148頁(yè) |

| 文件大?。?/td> | 1600K |

| 代理商: | MC68HC05JB3JDW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)當(dāng)前第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)

November 5, 1998

GENERAL RELEASE SPECIFICATION

MC68HC05JB3

RESETS

MOTOROLA

REV 1

5-3

The POR will generate the RST signal which will reset the CPU. If any other reset

function is active at the end of the 224 or 4064 cycle delay, the RST signal will

remain in the reset condition until the other reset condition(s) end.

POR will not activate the pulldown device on the RESET pin. VDD must drop

below VPOR in order for the internal POR circuit to detect the next rise of VDD.

5.3.2 USB Reset

The USB reset is generated by a detection on the USB bus reset signal. For

MC68HC05JB3, seeing a single-end zero on its upstream port for 4 to 8 bit times

will set RSTF bit in UIR0 register. The detections will also generate the RST signal

to reset the CPU and other peripherals in the MCU.

5.3.3 Computer Operating Properly (COP) Reset

The COP watchdog is enabled by a mask option.

A timeout of the COP watchdog generates a COP reset. The COP watchdog is

part of a software error detection system and must be cleared periodically to start

a new timeout period. To clear the COP watchdog and prevent a COP reset, write

a logic zero to the COPC bit of the COP register at location $1FF0.

COPC — COP Clear

COPC is a write-only bit. Periodically writing a logic zero to COPC prevents the

COP watchdog from resetting the MCU. Reset clears the COPC bit.

1 =

No effect on system.

0 =

Reset COP watchdog timer.

The COP Watchdog reset will assert the pull-down device to pull the RESET pin

low for one cycle of the internal bus clock.

Refer to section on Multi-Function Timer for detail on COP watchdog timeout peri-

ods.

5.3.4 Low Voltage Reset (LVR)

The LVR activates the RST reset signal to reset the device when the voltage on

the VDD pin falls below the LVR trip voltage. The LVR will assert the pulldown

device to pull the RESET pin low one cycle of the internal bus clock. The Low Volt-

age Reset circuit is enabled by a mask option.

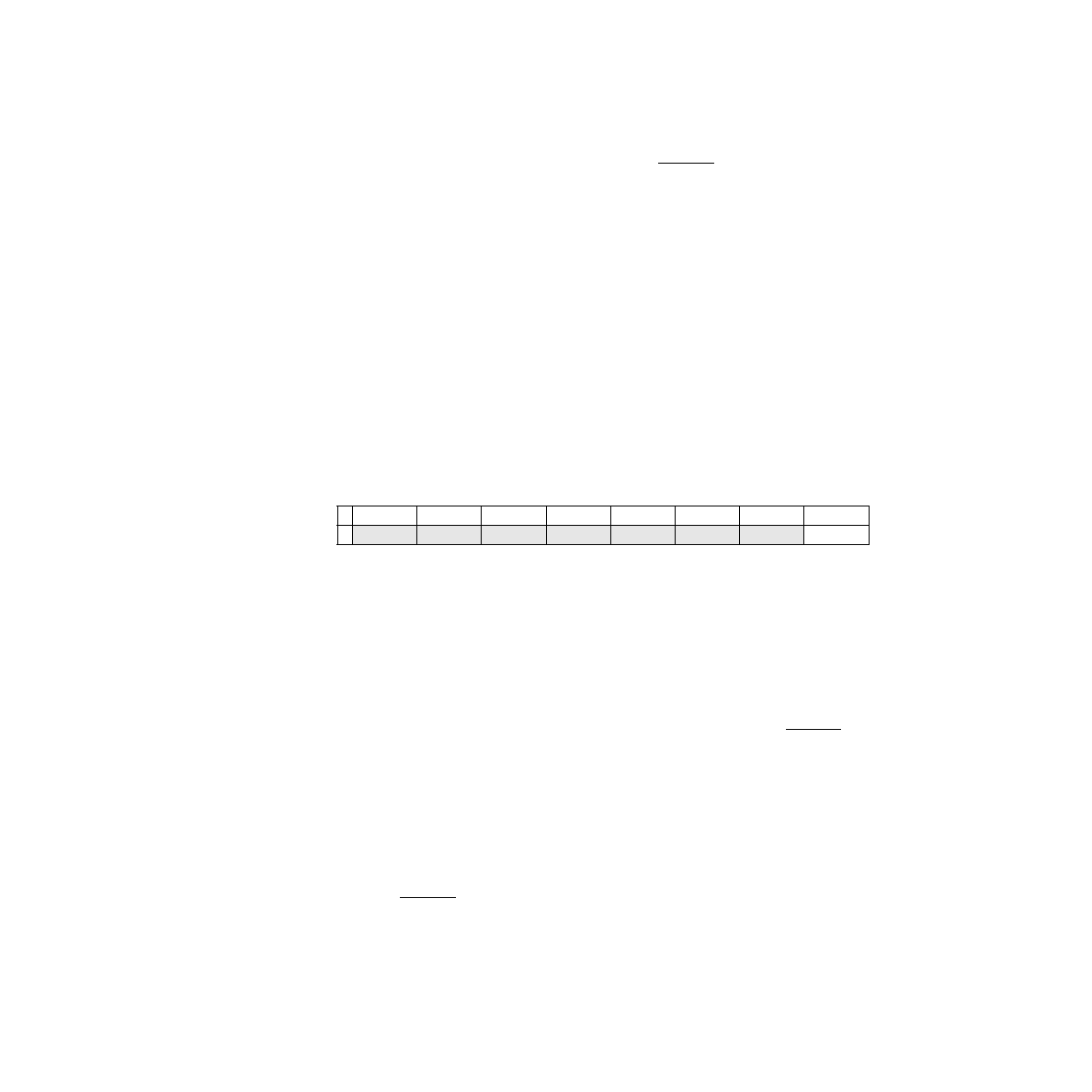

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

COPR

R

00000000

$1FF0

W

COPC

reset:

UUUUUUU

0

U = UNAFFECTED BY RESET

Figure 5-2. COP Watchdog Register (COPR)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC05JB3JP | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PDIP20 |

| MC68HC05K3CSD | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PDSO20 |

| MC68HC05K3P | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PDIP16 |

| MC68HC05L25PB | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PQFP52 |

| MC68HC05LJ5P | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PDIP16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC05JJ6 | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:General Release Specification Microcontrollers |

| MC68HC05JJ6CDW | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:General Release Specification Microcontrollers |

| MC68HC05JJ6CDWE | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:General Release Specification Microcontrollers |

| MC68HC05JJ6CP | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:General Release Specification Microcontrollers |

| MC68HC05JJ6CPE | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:General Release Specification Microcontrollers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。