- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377884 > MB8118160A-70 (Fujitsu Limited) CMOS 1M×16 BIT Fast Page Mode Dynamic RAM(CMOS 1M×16 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | MB8118160A-70 |

| 廠商: | Fujitsu Limited |

| 英文描述: | CMOS 1M×16 BIT Fast Page Mode Dynamic RAM(CMOS 1M×16 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| 中文描述: | 的CMOS 100萬(wàn)× 16位快速頁(yè)面模式動(dòng)態(tài)RAM的CMOS(100萬(wàn)× 16位快速頁(yè)面存取模式動(dòng)態(tài)內(nèi)存) |

| 文件頁(yè)數(shù): | 5/26頁(yè) |

| 文件大?。?/td> | 494K |

| 代理商: | MB8118160A-70 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)

5

MB8118160A-60/MB8118160A-70

I

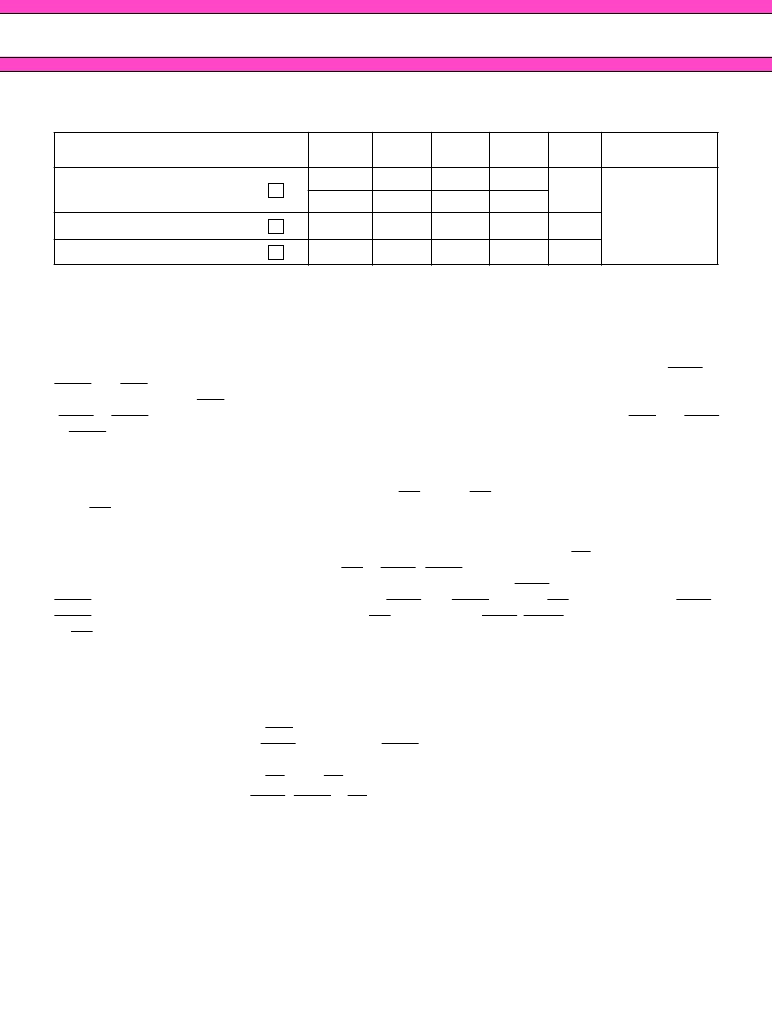

RECOMMENDED OPERATING CONDITIONS

* :Undershoots of up to –2.0 volts with a pulse width not exceeding 20 ns are acceptable.

I

FUNCTIONAL OPERATION

ADDRESS INPUTS

Twenty input bits are required to decode any sixteen of 16,777,216 cell addresses in the memory matrix. Since

only twelve address bits (A

0

to A

9

) are available, the column and row inputs are separately strobed by LCAS or

UCAS and RAS as shown in Figure 1. First, ten row address bits are input on pins A

0

-through-A

9

and latched with

the row address strobe (RAS) then, ten column address bits are input and latched with the column address strobe

(LCAS or UCAS). Both row and column addresses must be stable on or before the falling edges of RAS and LCAS

or UCAS, respectively. The address latches are of the flow-through type; thus, address information appearing after

t

RAH

(min.) + t

T

is automatically treated as the column address.

WRITE ENABLE

The read or write mode is determined by the logic state of WE. When WE is active Low, a write cycle is initiated;

when WE is High, a read cycle is selected. During the read mode, input data is ignored.

DATA INPUT

Input data is written into memory in either of three basic ways – an early write cycle, an OE (delayed) write cycle,

and a read-modify-write cycle. The falling edge of WE or LCAS / UCAS, whichever is later, serves as the input data-

latch strobe. In an early write cycle, the input data of DQ

1

-DQ

8

is strobed by LCAS and DQ

9

-DQ

16

is strobed by

UCAS and the setup/hold times are referenced to each LCAS and UCAS because WE goes Low before LCAS /

UCAS. In a delayed write or a read-modify-write cycle, WE goes Low after LCAS / UCAS; thus, input data is strobed

by WE and all setup/hold times are referenced to the write-enable signal.

DATA OUTPUT

The three-state buffers are TTL compatible with a fanout of two TTL loads. Polarity of the output data is identical

to that of the input; the output buffers remain in the high-impedance state until the column address strobe goes

Low. When a read or read-modify-write cycle is executed, valid outputs are obtained under the following conditions:

t

RAC

:

from the falling edge of RAS when t

RCD

(max.) is satisfied.

t

CAC

:

from the falling edge of LCAS (for DQ

1

-DQ

8

) UCAS (for DQ

9

-DQ

16

) when t

RCD

is greater than t

RCD

(max.).

t

AA

:

from column address input when t

RAD

is greater than t

RAD

(max.).

t

OEA

:

from the falling edge of OE when OE is brought Low after t

RAC

, t

CAC

, or t

AA

, and t

RCD

(max.) is satisfied.

The data remains valid until either LCAS / UCAS or OE returns to a High logic level. When an early write is executed,

the output buffers remain in a high-impedance state during the entire cycle.

Parameter

Notes

Symbol

Min.

Typ.

Max.

Unit

Ambient

Operating Temp.

Supply Voltage

V

CC

4.5

5.0

5.5

V

0

°

C to +70

°

C

V

SS

0.0

0.0

0.0

Input High Voltage, all inputs

V

IH

2.4

—

6.5

V

Input Low Voltage, all inputs*

V

IL

–0.3

—

0.8

V

1

1

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB8118165B-50 | CMOS 1M ×16 BIT Hyper Page Mode Dynamic RAM(CMOS 1M ×16 位超級(jí)頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB8118165B-60 | CMOS 1M ×16 BIT Hyper Page Mode Dynamic RAM(CMOS 1M ×16 位超級(jí)頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814100A-60 | CMOS 4 M ×1 BIT Fast Page Mode DRAM(CMOS 4M ×1 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814100A-70 | CMOS 4 M ×1 BIT Fast Page Mode DRAM(CMOS 4M ×1 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814100A-80 | CMOS 4 M ×1 BIT Fast Page Mode DRAM(CMOS 4M ×1 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB812 | 功能描述:ACCY MOUNT BMM 3/4 58A RoHS:是 類別:RF/IF 和 RFID >> RF配件 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* |

| MB812.833 | 功能描述:ACCY MOUNT BMM 3/4 58A RoHS:是 類別:RF/IF 和 RFID >> RF配件 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* |

| MB-8120 | 制造商:Maxxtro 功能描述: |

| MB81256-10 | 制造商:FUJITSU 功能描述:256K X 1 PAGE MODE DRAM, 100 ns, CQCC18 |

| MB81256-10P | 制造商:FUGITSU 功能描述:Dynamic RAM, Page Mode, 256K x 1, 16 Pin, Plastic, DIP 制造商:Fuji Electric 功能描述:Dynamic RAM, Page Mode, 256K x 1, 16 Pin, Plastic, DIP 制造商:FUJITSU 功能描述:Dynamic RAM, Page Mode, 256K x 1, 16 Pin, Plastic, DIP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。