- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369889 > M68HC001 (Motorola, Inc.) 16-/32-Bit Microprocessor(16/32位微處理器) PDF資料下載

參數(shù)資料

| 型號: | M68HC001 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 16-/32-Bit Microprocessor(16/32位微處理器) |

| 中文描述: | 16/32位微處理器(16/32位微處理器) |

| 文件頁數(shù): | 96/184頁 |

| 文件大小: | 1006K |

| 代理商: | M68HC001 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁當前第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁

MOTOROLA

M68000 8-/16-/32-BIT MICROPROCESSORS USER’S MANUAL

6-11

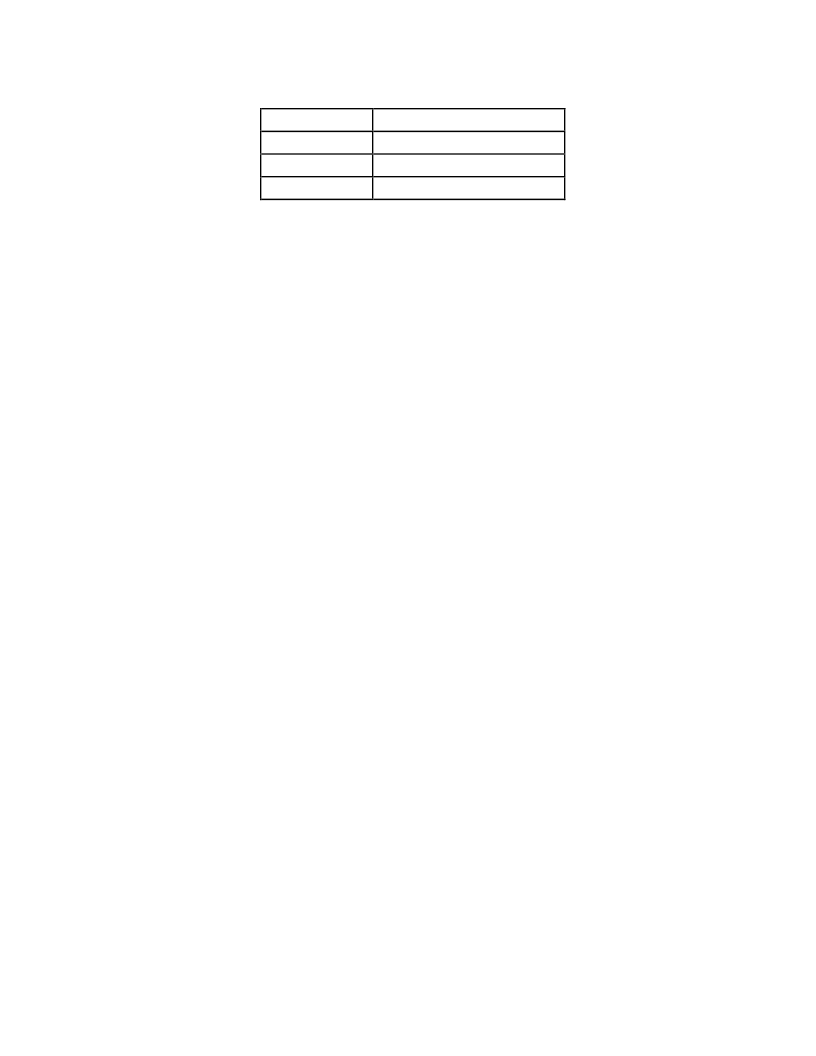

Table 6-4. MC68010 Format Codes

Format Code

Stacked Information

0000

Short Format (4 Words)

1000

Long Format (29 Words)

All Others

Unassigned, Reserved

6.2.5 Exception Processing Sequence

In the first step of exception processing, an internal copy is made of the status register.

After the copy is made, the S bit of the status register is set, putting the processor into the

supervisor mode. Also, the T bit is cleared, which allows the exception handler to execute

unhindered by tracing. For the reset and interrupt exceptions, the interrupt priority mask is

also updated appropriately.

In the second step, the vector number of the exception is determined. For interrupts, the

vector number is obtained by a processor bus cycle classified as an interrupt acknowledge

cycle. For all other exceptions, internal logic provides the vector number. This vector

number is then used to calculate the address of the exception vector.

The third step, except for the reset exception, is to save the current processor status. (The

reset exception does not save the context and skips this step.) The current program

counter value and the saved copy of the status register are stacked using the SSP. The

stacked program counter value usually points to the next unexecuted instruction.

However, for bus error and address error, the value stacked for the program counter is

unpredictable and may be incremented from the address of the instruction that caused the

error. Group 1 and 2 exceptions use a short format exception stack frame (format = 0000

on the MC68010). Additional information defining the current context is stacked for the bus

error and address error exceptions.

The last step is the same for all exceptions. The new program counter value is fetched

from the exception vector. The processor then resumes instruction execution. The

instruction at the address in the exception vector is fetched, and normal instruction

decoding and execution is started.

6.3 PROCESSING OF SPECIFIC EXCEPTIONS

The exceptions are classified according to their sources, and each type is processed

differently. The following paragraphs describe in detail the types of exceptions and the

processing of each type.

6.3.1 Reset

The reset exception corresponds to the highest exception level. The processing of the

reset exception is performed for system initiation and recovery from catastrophic failure.

Any processing in progress at the time of the reset is aborted and cannot be recovered.

The processor is forced into the supervisor state, and the trace state is forced off. The

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M68EC000 | 16/32 Bit Microprocesso(16/32位微處理器) |

| M68HC16 | 16-Bit Microcontroller(16位微控制器) |

| MAC08BT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

| MAC08MT1 | SENSITIVE GATE TRIACS |

| MAC08DT1 | TRIAC 0.8 AMPERE RMS 200 thru 600 Volts |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M68HC05 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| M68HC05_13 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC05 Microcontrollers |

| M68HC05EVS | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Motorola M68HC05 Family Evaluation System |

| M68HC05M68H | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HCMOS Microcontroller Unit |

| M68HC08 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復。