- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45037 > M37754S4CGP 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | M37754S4CGP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁(yè)數(shù): | 99/114頁(yè) |

| 文件大小: | 1116K |

| 代理商: | M37754S4CGP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)當(dāng)前第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)

85

PRELIMINAR

Y

Notice:

This

is not

a final

specification.

Some

parametric

limits

are

subject

to change.

MITSUBISHI MICROCOMPUTERS

M37754M8C-XXXGP, M37754M8C-XXXHP

M37754S4CGP, M37754S4CHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

tc(TB)

tw(TBH)

tw(TBL)

tc(TB)

tw(TBH)

tw(TBL)

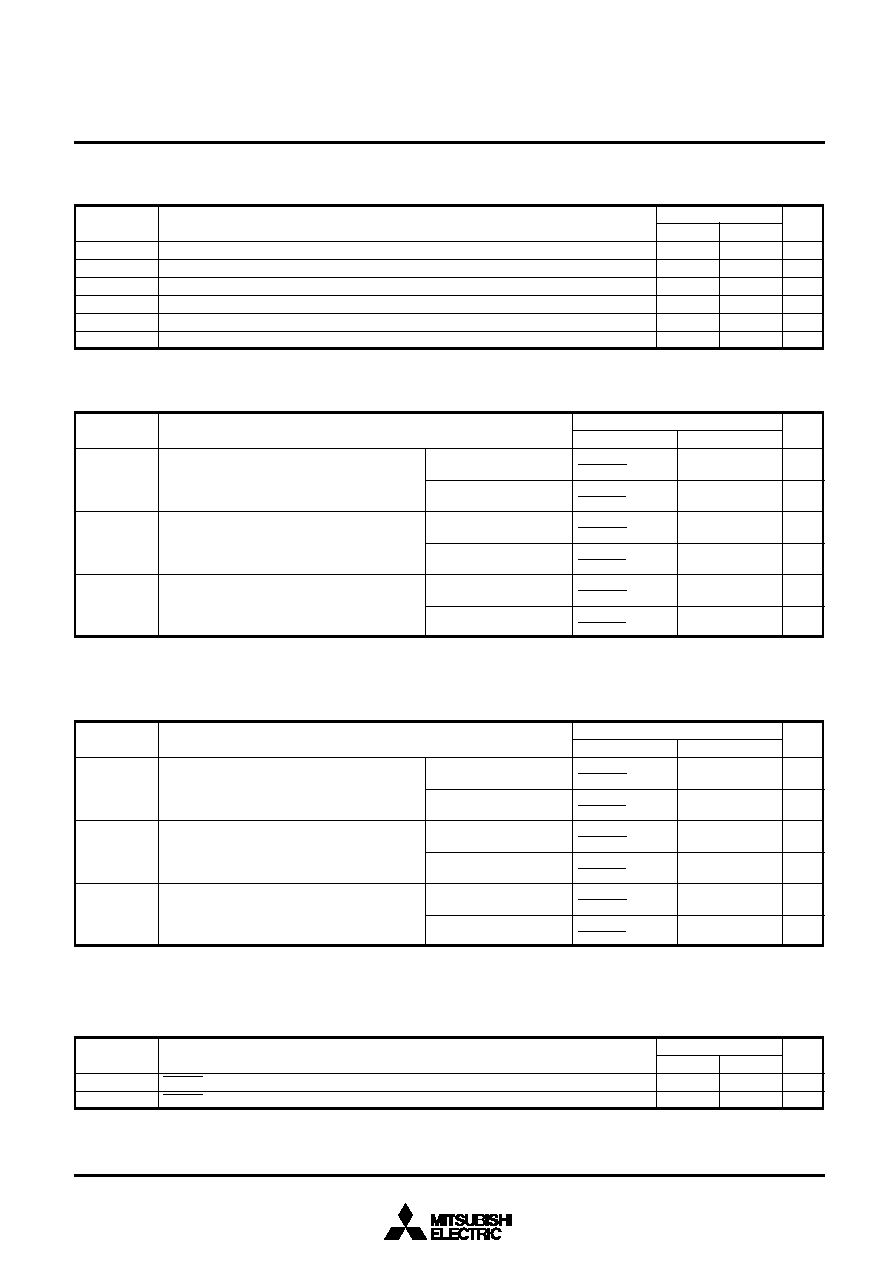

Timer B input (Count input in event counter mode)

Symbol

TBiIN input cycle time (one edge count)

TBiIN input high-level pulse width (one edge count)

TBiIN input low-level pulse width (one edge count)

TBiIN input cycle time (both edge count)

TBiIN input high-level pulse width (both edge count)

TBiIN input low-level pulse width (both edge count)

Parameter

Limits

Min.

80

40

160

80

Max.

ns

Unit

Limits

Symbol

Parameter

Min.

Max.

Unit

16

× 109

f(XIN)

8

× 109

f(XIN)

8

× 109

f(XIN)

4

× 109

f(XIN)

8

× 109

f(XIN)

4

× 109

f(XIN)

(400)

(320)

(200)

(160)

(200)

(160)

f(XIN)

≤ 40 MHz

f(XIN)

≤ 25 MHz

f(XIN)

≤ 40 MHz

f(XIN)

≤ 25 MHz

f(XIN)

≤ 40 MHz

f(XIN)

≤ 25 MHz

tc(TB)

tw(TBH)

tw(TBL)

TBiIN input cycle time

TBiIN input high-level pulse width

TBiIN input low-level pulse width

ns

Timer B input (Pulse period measurement mode)

Note : The TBiIN input cycle time requires 4 or more cycles of count source. The TBiIN input high-level pulse width and the TBiIN input low-level pulse width

respectively require 2 or more cycles of the count source. The limits in the table are the values when the count source is f(XIN)/4 in high-speed running

(f(XIN)

≤ 40 MHz) and when the count source is f(XIN)/2 in low-speed running (f(XIN) ≤ 25 MHz). At this time, the clock source select bit is “0.”

Limits

Symbol

Parameter

Min.

Max.

Unit

16

× 109

f(XIN)

8

× 109

f(XIN)

8

× 109

f(XIN)

4

× 109

f(XIN)

8

× 109

f(XIN)

4

× 109

f(XIN)

(400)

(320)

(200)

(160)

(200)

(160)

f(XIN)

≤ 40 MHz

f(XIN)

≤ 25 MHz

f(XIN)

≤ 40 MHz

f(XIN)

≤ 25 MHz

f(XIN)

≤ 40 MHz

f(XIN)

≤ 25 MHz

tc(TB)

tw(TBH)

tw(TBL)

TBiIN input cycle time

TBiIN input high-level pulse width

TBiIN input low-level pulse width

ns

Timer B input (Pulse width measurement mode)

Note : The TBiIN input cycle time requires 4 or more cycles of count source. The TBiIN input high-level pulse width and the TBiIN input low-level pulse width

respectively require 2 or more cycles of the count source. The limits in the table are the values when the count source is f(XIN)/4 in high-speed running

(f(XIN)

≤ 40 MHz) and when the count source is f(XIN)/2 in low-speed running (f(XIN) ≤ 25 MHz). At this time, the clock source select bit is “0.”

tc(AD)

tw(ADL)

Symbol

ADTRG input cycle time (minimum allowable trigger)

ADTRG input low-level pulse width

Parameter

Min.

1000

125

Limits

Max.

ns

Unit

A-D trigger input

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37754M8C-XXXHP | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37754S4CHP | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37754S4CHP | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37754M8C-XXXGP | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37777E9AGS | 16-BIT, UVPROM, 16 MHz, MICROCONTROLLER, CQCC100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37754S4CHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M3775PR-H400CL | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

| M3775RK-0.75A | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

| M3775RK-C0.50A | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

| M3775RK-C0.50B | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。