- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45037 > M37754S4CGP 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | M37754S4CGP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁(yè)數(shù): | 66/114頁(yè) |

| 文件大小: | 1116K |

| 代理商: | M37754S4CGP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)當(dāng)前第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)

55

PRELIMINAR

Y

Notice:

This

is not

a final

specification.

Some

parametric

limits

are

subject

to change.

MITSUBISHI MICROCOMPUTERS

M37754M8C-XXXGP, M37754M8C-XXXHP

M37754S4CGP, M37754S4CHP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

to “0” when reading the low-order byte of the receive buffer register

or when writing “0” to the REi flag or when setting to a parallel port.

The OERi and SUMi flags are cleared to “0” when writing “0” to the

REi flag or when setting to a parallel port.

The SUMi flag is cleared to “0” when the OERi, FERi, PERi flags are

cleared to “0” all.

Sleep mode

The sleep mode is used to communicate only between certain micro-

computers when multiple microcomputers are connected through se-

rial I/O.

The microcomputer enters the sleep mode when bit 7 of UARTi

Transmit/Receive mode register is set to “1.”

The operation of the sleep mode for an 8-bit asynchronous commu-

nication is described below.

When sleep mode is selected, the contents of the receive register is

not transferred to the receive buffer register if bit 7 (bit 6 if 7-bit asyn-

chronous communication and bit 8 if 9-bit asynchronous communica-

tion) of the received data is “0”. Also the RIi, OERi, FERi, PERi, and

the SUMi flag are unchanged. Therefore, the interrupt request bit of

the UARTi receive interrupt control register is also unchanged. Nor-

mal receive operation takes place when bit 7 of the received data is

“1”.

The following is an example of how the sleep mode can be used.

The main microcomputer first sends data: bit 7 is “1” and bits 0 to 6

are set to the address of the subordinate microcomputer to be com-

municated with. Then all subordinate microcomputers receive this

data. Each subordinate microcomputer checks the received data,

clears the sleep bit to “0” if bits 0 to 6 are its own address and sets

the sleep bit to “1” if not. Next, the main microcomputer sends data

with bit 7 cleared. Then the microcomputer which cleared the sleep

bit will receive the data, but the microcomputers which set the sleep

bit to “1” will not. In this way, the main microcomputer is able to com-

municate only with the designated microcomputer.

Receive

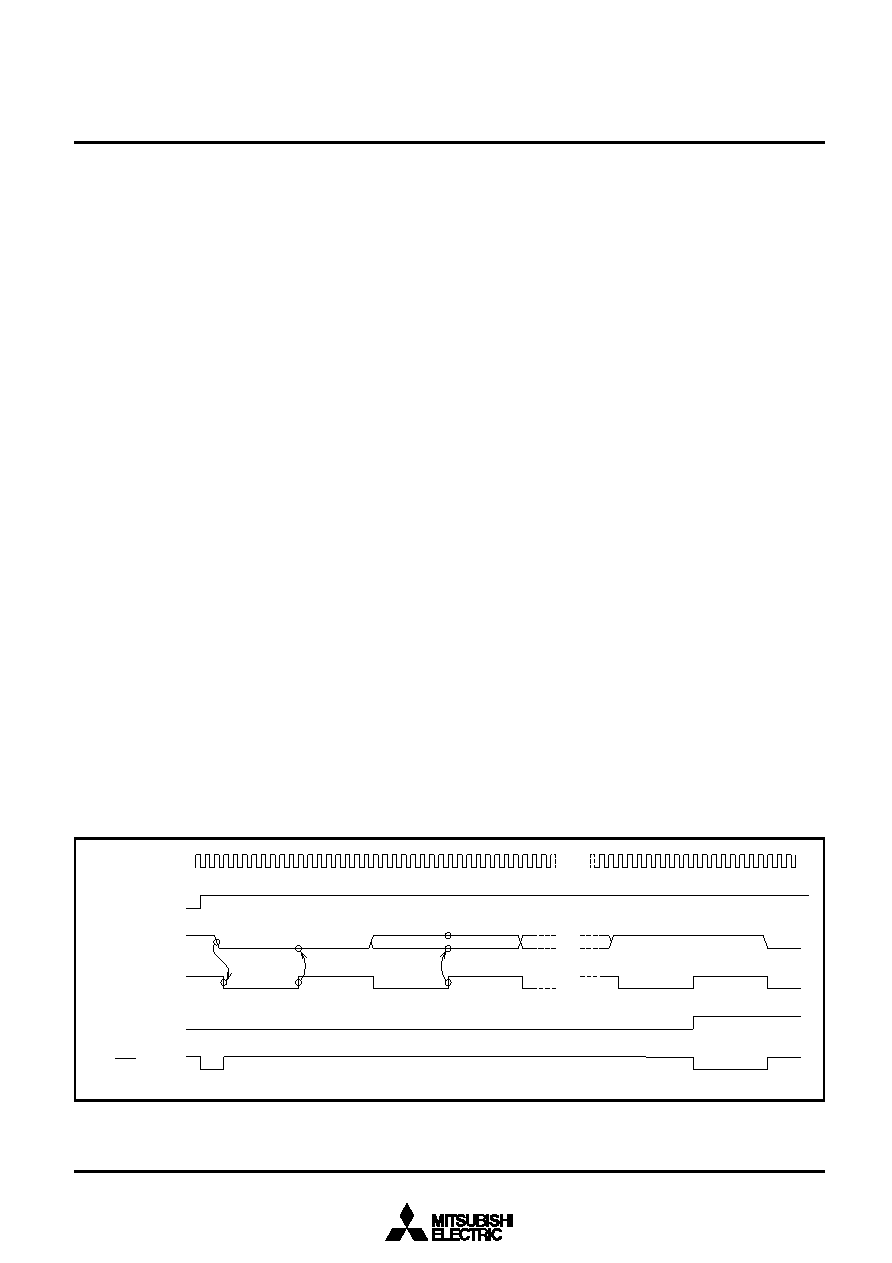

Receive is enabled when bit 2 (REi flag) of UARTi Transmit/Receive

control register 1 is set to “1.” As shown in Figure 67, the frequency

divider circuit (1/16) at the receiving side begin to work when a start

bit arrives and the data is received.

____

If RTSi output is selected by setting bit 2 of UARTi Transmit/Receive

____

control register 0 to “1”, the RTSi output is “H” when the REi flag is

____

“0”. When the REi flag changes to “1”, the RTSi output goes “L” to

indicate receive ready and returns to “H” once receive has started. In

____

other words, RTSi output can be used to determine externally

whether the receive register is ready to receive.

The entire transmission data bits are received when the start bit

passes the final bit of the receive block shown in Figure 56. At this

point, the contents of the receive register is transferred to the receive

buffer register and bit 3 (Rli flag) of UARTi Transmit/Receive control

register 1 is set to “1.” In other words, the RIi flag indicates that the

____

receive buffer register contains data when it is set to “1.” If RTSi out-

____

put is selected, RTSi output goes “L” to indicate that the register is

ready to receive the next data.

The interrupt request bit of the UARTi receive interrupt control regis-

ter is set to “1” when the RIi flag changes from “0” to “1”.

Bit 4 (OERi flag) of UARTi Transmit/Receive control register 1 is set

to “1” when the next data is transferred from the receive register to

the receive buffer register while the RIi flag is “1”, in other words,

when an overrun error occurs. If the OERi flag is “1”,

it indicates that the next data has been transferred to the receive

buffer register before the contents of the receive buffer register has

been read.

Bit 5 (FERi flag) is set to “1” when the number of stop bits is less than

required (framing error).

Bit 6 (PERi flag) is set to “1” when a parity error occurs.

Bit 7 (SUMi flag) is set to “1” when either the OERi flag, FERi flag, or

the PERi flag is set to “1.” Therefore, the SUMi flag can be used to

determine whether there is an error.

The setting of the RIi flag, OERi flag, FERi flag, and the PERi flag is

performed while transferring the contents of the receive register to

the receive buffer register. The Rli, FERi, and PERi flags are cleared

Fig. 67 Receive timing example when 8-bit asynchronous communication with no parity and 1 stop bit selected

Start bit

Stop bit

Start bit

D0

D1

D7

Check to be “L” level

Starting at the falling

edge of start bit

Data fetched

Pfi or fEXT

REi

RXDi

Receive

Clock

RIi

RTSi

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37754M8C-XXXHP | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37754S4CHP | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37754S4CHP | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37754M8C-XXXGP | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37777E9AGS | 16-BIT, UVPROM, 16 MHz, MICROCONTROLLER, CQCC100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37754S4CHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M3775PR-H400CL | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

| M3775RK-0.75A | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

| M3775RK-C0.50A | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

| M3775RK-C0.50B | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。