- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69014 > M37643M8-XXXHP 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | M37643M8-XXXHP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | 12 X 12 MM, 0.50 MM PITCH, PLASTIC, LQFP-80 |

| 文件頁數(shù): | 121/123頁 |

| 文件大小: | 1292K |

| 代理商: | M37643M8-XXXHP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁當(dāng)前第121頁第122頁第123頁

Rev.2.00

Aug 28, 2006

page 95 of 119

7643 Group

REJ03B0054-0200

Functions To Inhibit Rewriting Flash Memory

Version

To prevent the contents of internal flash memory from being read

out or rewritten easily, this MCU incorporates a ROM code protect

function for use in parallel I/O mode and an ID code check func-

tion for use in standard serial I/O mode.

qROM Code Protect Function (in Pararell I/O Mode)

The ROM code protect function is the function to inhibit reading

out or modifying the contents of internal flash memory by using

the ROM code protect control (address FFC916) in parallel I/O

mode. Figure 84 shows the ROM code protect control (address

FFC916). (This address exists in the User ROM area.)

If one or both of the pair of ROM Code Protect Bits is set to “0”,

the ROM code protect is turned on, so that the contents of internal

flash memory are protected against readout and modification. The

ROM code protect is implemented in two levels. If level 2 is se-

lected, the flash memory is protected even against readout by a

shipment inspection LSI tester, etc. When an attempt is made to

select both level 1 and level 2, level 2 is selected by default.

If both of the two ROM Code Protect Reset Bits are set to “00”, the

ROM code protect is turned off, so that the contents of internal

flash memory can be read out or modified. Once the ROM code

protect is turned on, the contents of the ROM Code Protect Reset

Bits cannot be modified in parallel I/O mode. Use the serial I/O or

CPU rewrite mode to rewrite the contents of the ROM Code Pro-

tect Reset Bits.

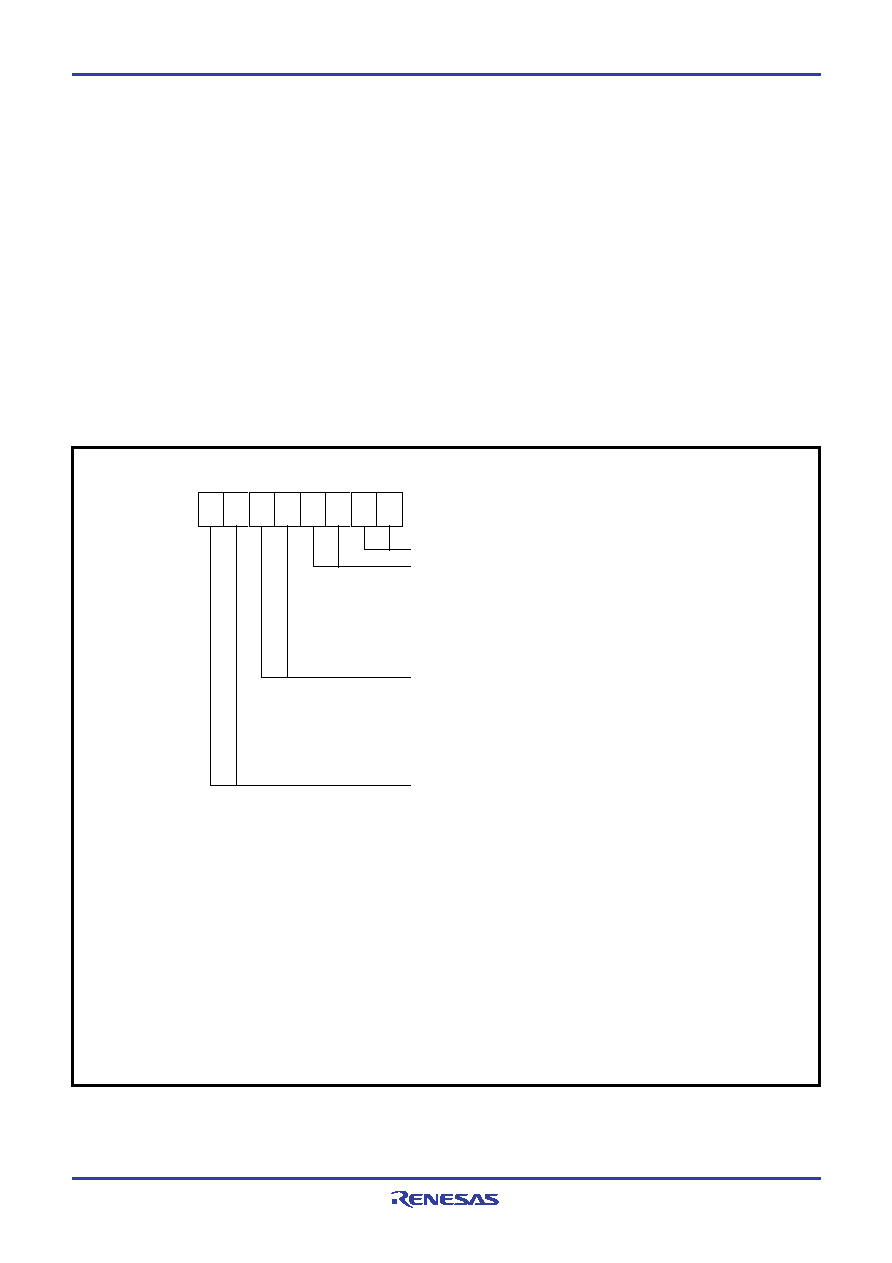

Fig. 84 Structure of ROM code protect control

ROM code protect control (address FFC916) (Note 1)

ROMCP

Reserved bits (“1” at read/write)

ROM code protect level 2 set bits (ROMCP2) (Notes 2, 3)

b3b2

0 0: Protect enabled

0 1: Protect enabled

1 0: Protect enabled

1 1: Protect disabled

ROM code protect reset bits (Note 4)

b5b4

0 0: Protect removed

0 1: Protect set bits effective

1 0: Protect set bits effective

1 1: Protect set bits effective

ROM code protect level 1 set bits (ROMCP1) (Note 2)

b7b6

0 0: Protect enabled

0 1: Protect enabled

1 0: Protect enabled

1 1: Protect disabled

b0

b7

Notes1: This area is on the ROM in the mask ROM version.

2: When ROM code protect is turned on, the internal flash memory is protected

against readout or modification in parallel I/O mode.

3: When ROM code protect level 2 is turned on, ROM code readout by a shipment

inspection LSI tester, etc. also is inhibited.

4: The ROM code protect reset bits can be used to turn off ROM code protect level 1

and ROM code protect level 2. However, since these bits cannot be modified in

parallel I/O mode, they need to be rewritten in standard serial I/O mode or CPU

rewrite mode.

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37643F8HP | 8-BIT, FLASH, 12 MHz, MICROCONTROLLER, PQFP80 |

| M37700E2AFS | 16-BIT, UVPROM, 16 MHz, MICROCONTROLLER, CQCC80 |

| M37700E2AXXXFP | 16-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQFP80 |

| M37701E2-XXXSP | 16-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP64 |

| M37702E4EXXXFP | 16-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PQFP80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M3764A-12 | 制造商:OK International 功能描述: |

| M3765 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:HORN/SIREN WITH SOFT CHIRP 6 ALARM SOUNDS |

| M3766 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:HORN/SIREN WITH SOFT CHIRP 6 ALARM SOUNDS |

| M37702E2LGP | 制造商:Mitsubishi Electric 功能描述: |

| M37702E4BFS | 制造商:Renesas Electronics Corporation 功能描述:EPROM MCU/8BIT CMOS EMULATION CHIP - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。