- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369885 > LXT388LE PCM TRANSCEIVER|DUAL|CEPT PCM-30/E-1|CMOS|QFP|100PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | LXT388LE |

| 英文描述: | PCM TRANSCEIVER|DUAL|CEPT PCM-30/E-1|CMOS|QFP|100PIN|PLASTIC |

| 中文描述: | 的PCM收發(fā)器|雙|優(yōu)稅PCM-30/E-1 |的CMOS | QFP封裝| 100引腳|塑料 |

| 文件頁數(shù): | 19/80頁 |

| 文件大小: | 1112K |

| 代理商: | LXT388LE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Octal T1/E1/J1 Transceiver

—

LXT384

Datasheet

19

84

84

84

84

J14

J14

J14

J14

DS

WR

SDI

LEN0

DI

DI

DI

DI

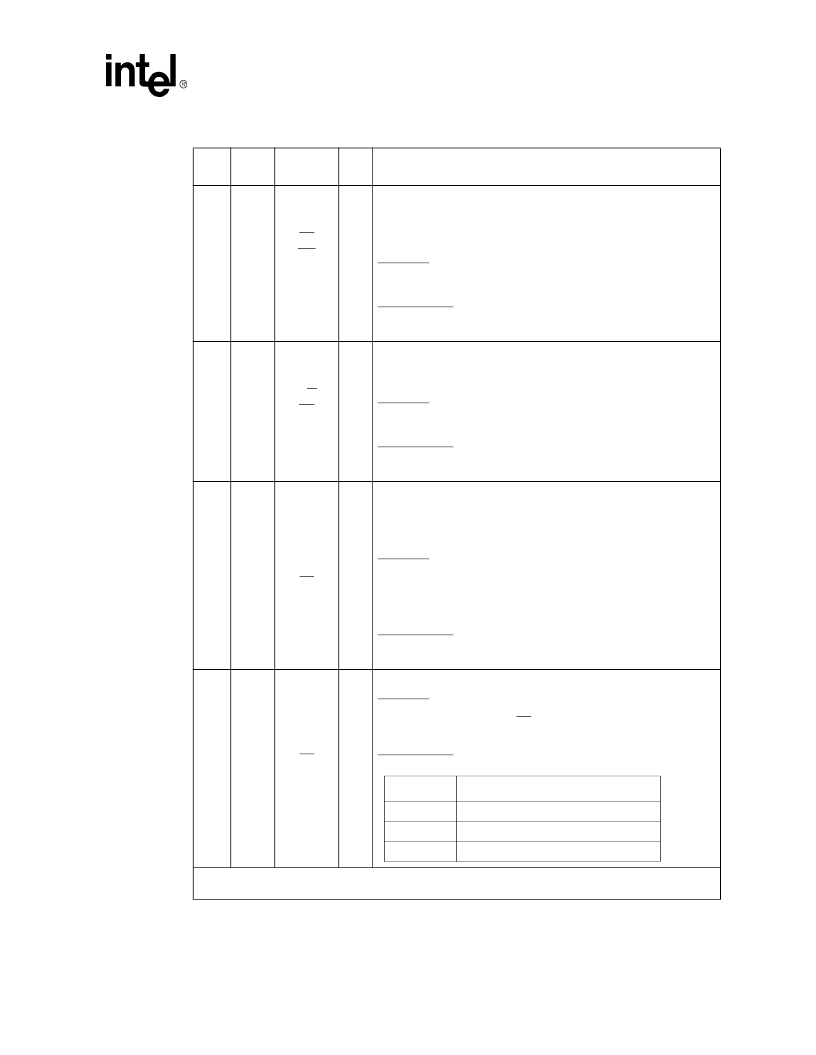

Data Strobe Input (Motorola Mode).

Write Enable Input (Intel mode).

Serial Data Input (Serial Mode).

Line Length Equalizer Input (Hardware Mode).

Host Mode

This pin acts as data strobe in Motorola mode and as Write Enable in

Intel mode. In serial mode, this pin is used as Serial Data Input.

Hardware Mode

This pin determines the shape and amplitude of the transmit pulse.

Please refer to

Table 2

.

85

85

85

J13

J13

J13

R/W

RD

LEN1

DI

DI

DI

Read/Write Input (Motorola Mode).

Read Enable Input (Intel Mode).

Line Length Equalizer Input (Hardware Mode).

Host Mode

This pin functions as the read/write signal in Motorola mode and as the

Read Enable in Intel mode.

Hardware Mode

This pin determines the shape and amplitude of the transmit pulse.

Please refer to

Table 2

.

86

86

86

86

J12

J12

J12

J12

ALE

SCLK

AS

LEN2

DI

DI

DI

DI

Address Latch Enable Input.

Shift Clock Input (Serial Mode).

Address Strobe (Motorola Mode).

Line Length Equalizer Input (Hardware Mode).

Host Mode

The address on the multiplexed address/data bus is clocked into the

device with the falling edge of ALE.

In serial Host mode, this pin acts as serial shift clock.

In Motorola mode, this pin acts a active Low address strobe.

Hardware Mode

This pin determines the shape and amplitude of the transmit pulse.

Please refer to

Table 2

.

87

87

J11

J11

CS

JASEL

DI

Chip Select/Jitter Attenuator Select Input

.

Host Mode

This active Low input is used to access the serial/parallel interface. For

each read or write operation, CS must transition from High to Low, and

remain Low.

Hardware Mode

This input determines the Jitter Attenuator position:

Table 1. LXT384 Pin Description (Sheet 9 of 12)

Pin #

QFP

Ball #

PBGA

Symbol

I/O

1

Description

1. DI: Digital Input; DO: Digital Output; DI/O: Digital Bidirectional Port; AI: Analog Input; AO: Analog Output

S: Power Supply; N.C.: Not Connected.

JASEL

JA Position

L

Transmit Path

H

Receive Path

Z

Disabled

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT400JE | Hermetically Sealed, 3.3V, High Speed, High CMR, Logic Gate Optocoupler |

| LXT6155LE | Telecomm/Datacomm |

| LXT6251A | ATM/SONET MAPPER|CMOS|QFP|208PIN|PLASTIC |

| LXT903PC | LAN Transceiver |

| LXT905LC | Laser Mouse VCSEL Assembly Clip |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT400 | 制造商:LVL1 制造商全稱:LVL1 功能描述:All Rate Extended Range Switched 56/DDS Transceiver |

| LXT400JE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Transceiver Circuit For Telecommunications |

| LXT441 | 制造商:LVL1 制造商全稱:LVL1 功能描述:Switched 56/DDS Integrated DSU/CSU |

| LXT6155 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:155 Mbps SDH/SONET/ATM Transceiver |

| LXT6155LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。