- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369873 > LV8572AVX Real-Time Clock PDF資料下載

參數(shù)資料

| 型號: | LV8572AVX |

| 英文描述: | Real-Time Clock |

| 中文描述: | 實(shí)時時鐘 |

| 文件頁數(shù): | 12/24頁 |

| 文件大小: | 353K |

| 代理商: | LV8572AVX |

Functional Description

(Continued)

the chip is unlocked, but only after another 30

m

s min

x

63

m

s max debounce time. The system designer must en-

sure that his system is stable when power has returned.

The power fail circuitry contains active linear circuitry that

draws supply current from V

CC

. In some cases this may be

undesirable, so this circuit can be disabled by masking the

power fail interrupt. The power fail input can perform all

lock-out functions previously mentioned, except that no ex-

ternal interrupt will be issued. Note that the linear power fail

circuitry is switched off automatically when using V

BB

in

standby mode.

LOW BATTERY, INITIAL POWER ON DETECT, AND

POWER FAIL TIME SAVE

There are three other functions provided on the LV8571A to

ease power supply control. These are an initial Power On

detect circuit, which also can be used as a time keeping

failure detect, a low battery detect circuit, and a time save

on power failure.

On initial power up the Oscillator Fail Flag will be set to a

one and the real time clock start bit reset to a zero. This

indicates that an oscillator fail event has occurred, and time

keeping has failed.

The Oscillator Fail flag will not be reset until the real-time

clock is started. This allows the system to discriminate be-

tween an initial power-up and recovery from a power failure.

If the battery backed mode is selected, then bit D6 of the

Periodic Flag Register must be written low. This will not af-

fect the contents of the Oscillator Fail Flag.

Another status bit is the low battery detect. This bit is set

only when the clock is operating under the V

CC

pin, and

when the battery voltage is determined to be less than 2.1V

(typical). When the power fail interrupt enable bit is low, it

disables the power fail circuit and will also shut off the low

battery voltage detection circuit as well.

To relieve CPU overhead for saving time upon power failure,

the Time Save Enable bit is provided to do this automatical-

ly. (See also Reading the Clock: Latched Read.) The Time

Save Enable bit, when set, causes the Time Save RAM to

follow the contents of the clock. This bit can be reset by

software, but if set before a power failure occurs, it will auto-

matically be reset when the clock switches to the battery

supply (not when a power failure is detected by the PFAIL

pin). Thus, writing a one to the Time Save bit enables both a

software write or power fail write.

SINGLE POWER SUPPLY APPLICATIONS

The LV8571A can be used in a single power supply applica-

tion. To achieve this, the V

BB

pin must be connected to

ground, and the power connected to V

CC

and PFAIL pins.

The Oscillator Failed/Single Supply bit in the Periodic Flag

Register should be set to a logic 1, which will disable the

oscillator battery reference circuit. The power fail interrupt

should also be disabled. This will turn off the linear power

fail detection circuits, and will eliminate any quiescent power

drawn through these circuits. Until the crystal select bits are

initialized, the LV8571A may consume about 50

m

A due to

arbitrary oscillator selection at power on.

(This extra 50

m

A is not consumed if the battery backed

mode is selected).

TIMER FUNCTIONAL DESCRIPTION

The LV8571A contains 2 independent multi-mode timers.

Each timer is composed of a 16-bit negative edge triggered

binary down counter and associated control. The operation

is similar to existing

m

P peripheral timers except that several

features have been enhanced. The timers can operate in

four modes, and in addition, the input clock frequency can

be selected from a prescaler over a wide range of frequen-

cies. Furthermore, these timers are capable of generating

interrupts and the Timer 0 output signal is available as a

hardware output via the MFO pin. Timer 1 output, however,

is not available as a hardware output signal. Both the inter-

rupt and MFO outputs are fully programmable active high, or

low, open drain, or push-pull.

Figure 7 shows the functional block diagram of one of the

timers. The timer consists of a 16-bit counter, two 8-bit input

registers, two 8-bit output registers, clock prescaler, mode

control logic, and output control logic. The timer and the

data registers are organized as two bytes for each timer.

Under normal operations a read/write to the timer locations

will read or write to the data input register. The timer con-

tents can be read by setting the counter Read bit (RD) in the

timer control register.

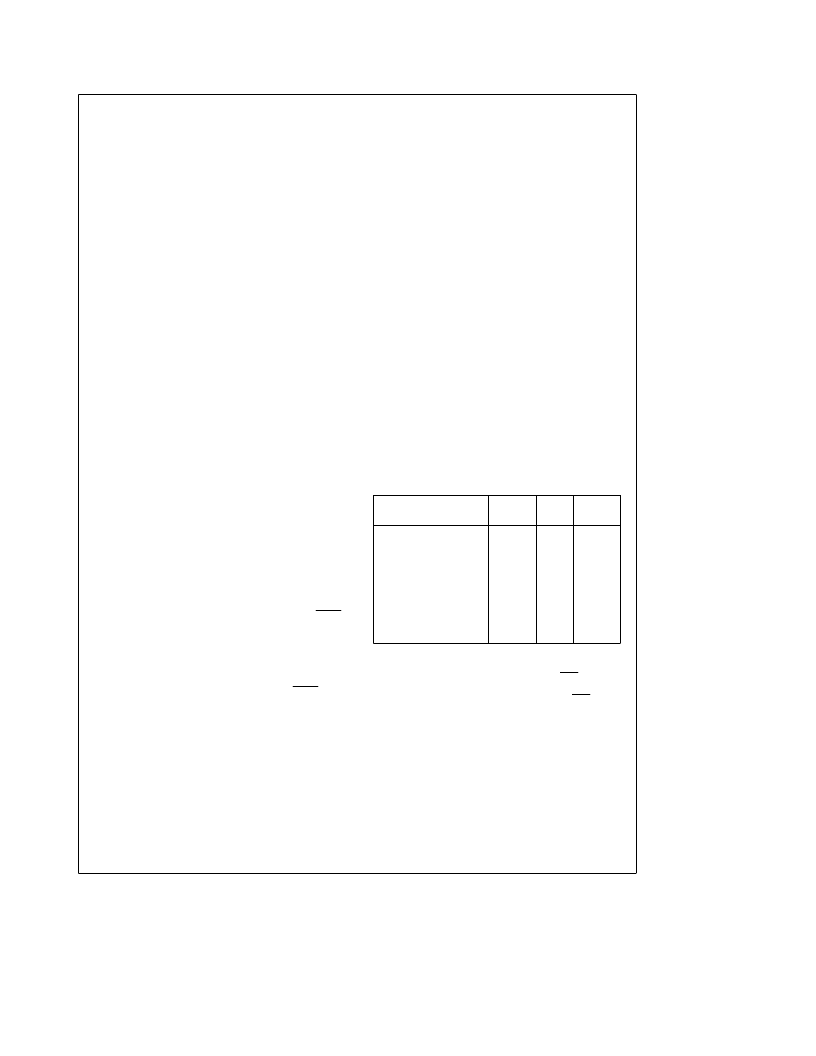

TIMER INITIALIZATION

The timer’s operation is controlled by a set of registers, as

listed in Table III. These consist of 2 data input registers and

one control register per timer. The data input registers con-

tain the timers count down value. The Timer Control Regis-

ter is used to set up the mode of operation and the input

clock rate. The timer related interrupts can be controlled by

programming the Interrupt Routing Register and Interrupt

Control Register 0. The timer outputs are configured by the

Output Mode Register.

TABLE III. Timer Associated Registers

Register Name

Register

Select

Page

Select

Address

Timer 0 Data MSB

Timer 0 Data LSB

Timer 0 Control Register

Timer 1 Data MSB

Timer 1 Data LSB

Timer 1 Control Register

Interrupt Routing Register

Interrupt Control Reg. 0

Output Mode Register

X

X

0

X

X

0

0

1

1

0

0

0

0

0

0

0

0

0

10H

0FH

01H

12H

11H

02H

04H

03H

02H

All these registers must be initialized prior to starting the

timer(s). The Timer Control Register should first be set to

select the timer mode with the timer start/stop bit reset.

Then when the timer is to be started the control register

should be rewritten identically but with the start/stop bit set.

TIMER OPERATION

Each timer is capable of operation in one of four modes. As

mentioned, these modes are programmed in each timer’s

Control Register which is described later. All four modes

operate in a similar manner. They operate on the two 8-bit

data words stored into the Data Input Register. At the begin-

ning of a counting cycle the 2 bytes are loaded into the timer

and the timer commences counting down towards zero. The

exact action taken when zero is reached depends on the

mode selected, but in general, the timer output will change

state, and an interrupt will be generated if the timer inter-

rupts are unmasked.

12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LV8800C | Optoelectronic |

| LVA12D | Analog IC |

| LVA12S | Analog IC |

| LVA15D | Analog IC |

| LVA15S | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LV8573A | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LV8573A Low Voltage Real Time Clock (RTC) |

| LV8573AM | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LV8573A Low Voltage Real Time Clock (RTC) |

| LV8573AN | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LV8573A Low Voltage Real Time Clock (RTC) |

| LV8573AV | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LV8573A Low Voltage Real Time Clock (RTC) |

| LV8573M | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LV8573A Low Voltage Real Time Clock (RTC) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。