- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358741 > LAN8700 (SMSC Corporation) 【15kV ESD Protected MII/RMII Fast-Ethernet PHY with HP Auto-MDIX and SMSC flexPWR TM in a Small Footprint PDF資料下載

參數(shù)資料

| 型號: | LAN8700 |

| 廠商: | SMSC Corporation |

| 英文描述: | 【15kV ESD Protected MII/RMII Fast-Ethernet PHY with HP Auto-MDIX and SMSC flexPWR TM in a Small Footprint |

| 中文描述: | 【15kV的ESD保護(hù)信息產(chǎn)業(yè)部/ RMII快速的HP Auto - MDIX功能和SMSC flexPWR商標(biāo)以太網(wǎng)PHY在小尺寸 |

| 文件頁數(shù): | 49/73頁 |

| 文件大小: | 457K |

| 代理商: | LAN8700 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

±15kV ESD Protected MII/RMII Fast-Ethernet PHY with HP Auto-MDIX and SMSC flexPWR

TM

in a Small Footprint

Datasheet

SMSC LAN8700/LAN8700I

49

Revision 1.0 (02-09-07)

DATASHEET

To de-assert the nINT interrupt output, either.

1. Clear the ENERGYON bit (17.1), by removing the cable, then writing a ‘1’ to register 29.7.

Or

2. Clear the Mask bit 30.1 by writing a ‘0’ to 30.1.

Note:

The ENERGYON bit 17.1 is defaulted to a ‘1’ at the start of the signal acquisition process,

therefore the Interrupt source flag 29.7 will also read as a ‘1’ at power-up. If no signal is

present, then both 17.1 and 29.7 wil clear within a few milliseconds.

5.4

Miscellaneous Functions

5.4.1

Carrier Sense

The carrier sense is output on CRS. CRS is a signal defined by the MII specification in the IEEE 802.3u

standard. The PHY asserts CRS based only on receive activity whenever the PHY is either in repeater

mode or full-duplex mode. Otherwise the PHY asserts CRS based on either transmit or receive activity.

The carrier sense logic uses the encoded, unscrambled data to determine carrier activity status. It

activates carrier sense with the detection of 2 non-contiguous zeros within any 10 bit span. Carrier

sense terminates if a span of 10 consecutive ones is detected before a /J/K/ Start-of Stream Delimiter

pair. If an SSD pair is detected, carrier sense is asserted until either /T/R/ End–of-Stream Delimiter

pair or a pair of IDLE symbols is detected. Carrier is negated after the /T/ symbol or the first IDLE. If

/T/ is not followed by /R/, then carrier is maintained. Carrier is treated similarly for IDLE followed by

some non-IDLE symbol.

5.4.2

Collision Detect

A collision is the occurrence of simultaneous transmit and receive operations. The COL output is

asserted to indicate that a collision has been detected. COL remains active for the duration of the

collision. COL is changed asynchronously to both RX_CLK and TX_CLK. The COL output becomes

inactive during full duplex mode.

COL may be tested by setting register 0, bit 7 high. This enables the collision test. COL will be asserted

within 512 bit times of TX_EN rising and will be de-asserted within 4 bit times of TX_EN falling.

In 10M mode, COL pulses for approximately 10 bit times (1us), 2us after each transmitted packet (de-

assertion of TX_EN). This is the Signal Quality Error (SQE) signal and indicates that the transmission

was successful. The user can disable this pulse by setting bit 11 in register 27.

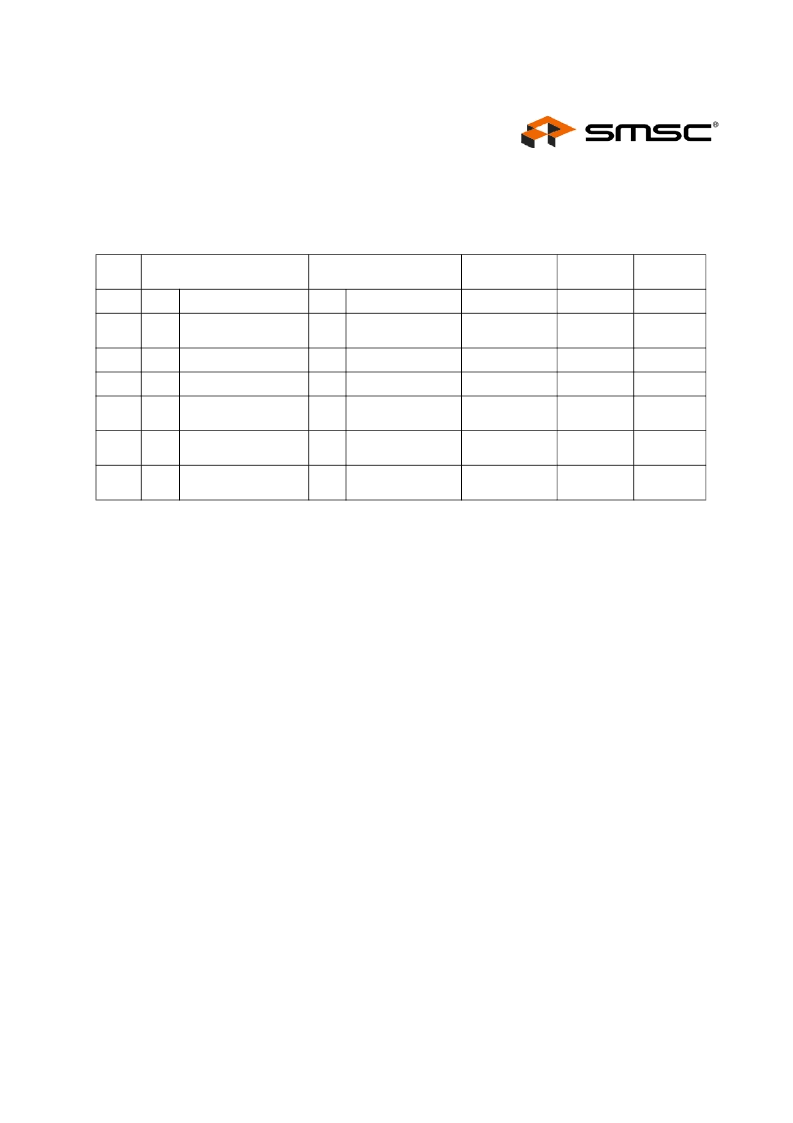

Table 5.46 Alternative Interrupt System Management Table.

Mask

Interrupt Source Flag

Interrupt Source

Event to Assert

nINT

Condition to

De-Assert.

Bit to Clear

nINT

30.7

29.7

ENERGYON

17.1

ENERGYON

Rising 17.1

17.1 low

29.7

30.6

29.6

Auto-Negotiation

complete

1.5

Auto-Negotiate

Complete

Rising 1.5

1.5 low

29.6

30.5

29.5

Remote Fault Detected

1.4

Remote Fault

Rising 1.4

1.4 low

29.5

30.4

29.4

Link Down

1.2

Link Status

Falling 1.2

1.2 high

29.4

30.3

29.3

Auto-Negotiation LP

Achnowledge

5.14

Acknowledge

Rising 5.14

5.14 low

29.3

30.2

29.2

Parallel Detection Fault

6.4

Parallel Detection

Fault

Rising 6.4

6.4 low

29.2

30.1

29.1

Auto-Negotiation Page

Received

6.1

Page Received

Rising 6.1

6.1 low

29.1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN9115 | HIGHLY EFFICIENT SINGLE - CHIP 10/100 NON PCI ETHERNET CONTROLLER |

| LAN9115-MD | HIGHLY EFFICIENT SINGLE - CHIP 10/100 NON PCI ETHERNET CONTROLLER |

| LAN9115-MT | HIGHLY EFFICIENT SINGLE - CHIP 10/100 NON PCI ETHERNET CONTROLLER |

| LAN9116 | Highly Efficient Single-Chip 10/100 Non-PCI Ethernet Controller |

| LAN9117 | HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN8700AEZG | 制造商:SMSC 功能描述: |

| LAN8700-AEZG | 功能描述:以太網(wǎng) IC HIPERFRM ETHRNT PHY RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN8700C-AEZG | 功能描述:以太網(wǎng) IC IC w/HP Auto-MDIX Embedded Ethernet RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN8700C-AEZG-AR2 | 制造商:Microchip Technology Inc 功能描述: 制造商:Microchip Technology Inc 功能描述:MII/RMII 10/100 ETHERNET TRANSCEIVER - Trays 制造商:Microchip Technology Inc 功能描述:TXRX ETHERNET 10/100 36-VQFN 制造商:Microchip Technology Inc 功能描述:Ethernet ICs MII/RMII 10/100 制造商:Microchip Technology Inc 功能描述:MII/RMII 10/100 Ethernet Transceiver, 36 VQFN 6x6x0.9 TRAY |

| LAN8700C-AEZG-TR | 功能描述:以太網(wǎng) IC Hi Perform Ethernet PHY RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。