- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373155 > KM418RD4AD (SAMSUNG SEMICONDUCTOR CO. LTD.) 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM PDF資料下載

參數(shù)資料

| 型號(hào): | KM418RD4AD |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| 中文描述: | 128/144Mbit RDRAM的256 × 16/18位× 2 * 16屬銀行直接RDRAMTM |

| 文件頁數(shù): | 57/64頁 |

| 文件大?。?/td> | 4052K |

| 代理商: | KM418RD4AD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁當(dāng)前第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Page 54

KM416RD8AC(D)/KM418RD8AC(D)

Direct RDRAM

Rev. 1.01 Oct. 1999

Timing Parameters

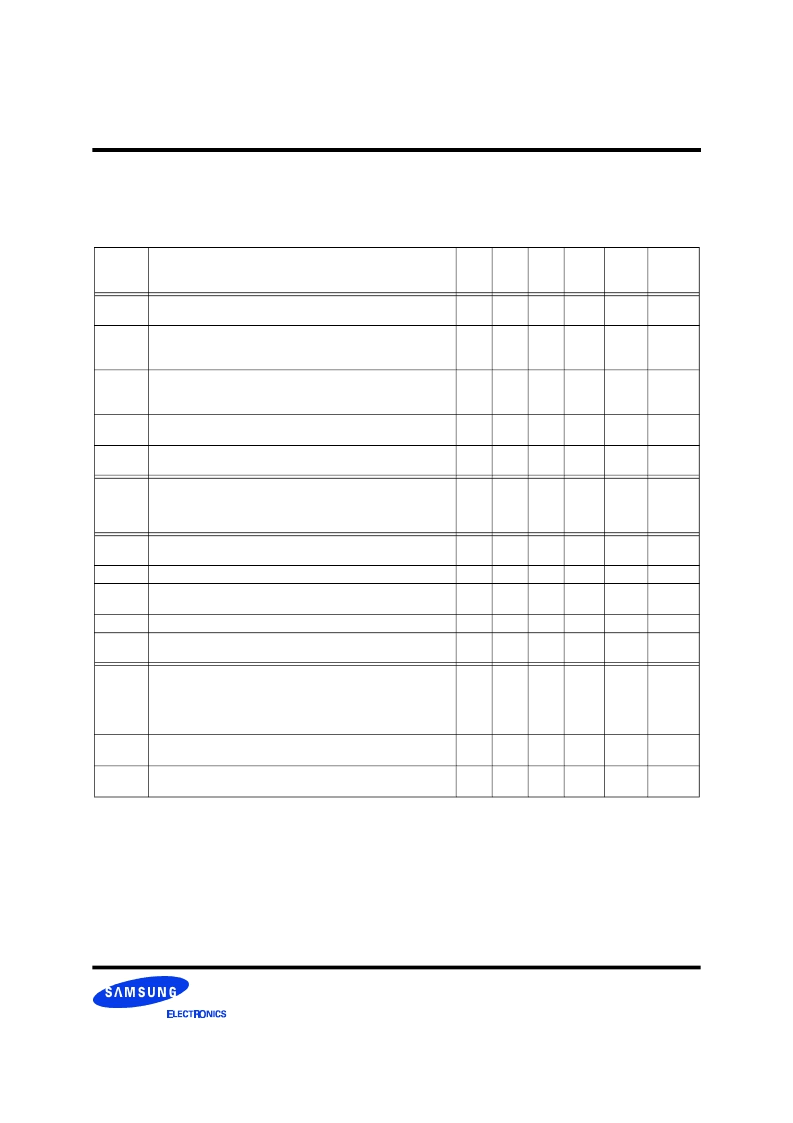

Table 22: Timing Parameter Summary

Parameter

Description

Min

-45

-800

Min

-45

-711

Min

-53.3

-600

Max

Units

Figure(s)

t

RC

Row Cycle time of RDRAM banks -the interval between ROWA packets with

ACT commands to the same bank.

28

28

28

-

t

CYCLE

Figure 15

Figure 16

t

RAS

RAS-asserted time of RDRAM bank - the interval between ROWA packet

with ACT command and next ROWR packet with PRER

a

command to the

same bank.

20

20

20

64

μ

s

b

t

CYCLE

Figure 15

Figure 16

t

RP

Row Precharge time of RDRAM banks - the interval between ROWR packet

with PRER

a

command and next ROWA packet with ACT command to the

same bank.

8

8

8

-

t

CYCLE

Figure 15

Figure 16

t

PP

Precharge-to-precharge time of RDRAM device - the interval between succes-

sive ROWR packets with PRER

a

commands to any banks of the same device.

8

8

8

-

t

CYCLE

Figure 12

t

RR

RAS-to-RAS time of RDRAM device - the interval between successive

ROWA packets with ACT commands to any banks of the same device.

8

8

8

-

t

CYCLE

Figure 13

t

RCD

RAS-to-CAS Delay - the interval from ROWA packet with ACT command to

COLC packet with RD or WR command). Note - the RAS-to-CAS delay seen

by the RDRAM core (t

RCD-C

) is equal to t

RCD-C

= 1 + t

RCD

because of differ-

ences in the row and column paths through the RDRAM interface.

9

7

7

-

t

CYCLE

Figure 15

Figure 16

t

CAC

CAS Access delay - the interval from RD command to Q read data. The equa-

tion for t

CAC

is given in the TPARM register in Figure 39.

8

8

8

12

t

CYCLE

Figure 4

Figure 39

t

CWD

CAS Write Delay (interval from WR command to D write data.

6

6

6

6

t

CYCLE

Figure 4

t

CC

CAS-to-CAS time of RDRAM bank - the interval between successive COLC

commands).

4

4

4

-

t

CYCLE

Figure 15

Figure 16

t

PACKET

Length of ROWA, ROWR, COLC, COLM or COLX packet.

4

4

4

4

t

CYCLE

Figure 3

t

RTR

Interval from COLC packet with WR command to COLC packet which causes

retire, and to COLM packet with bytemask.

8

8

8

-

t

CYCLE

Figure 17

t

OFFP

The interval (offset) from COLC packet with RDA command, or from COLC

packet with retire command (after WRA automatic precharge), or from COLC

packet with PREC command, or from COLX packet with PREX command to

the equivalent ROWR packet with PRER. The equation for t

OFFP

is given in

the TPARM register in Figure 39.

4

4

4

4

t

CYCLE

Figure 14

Figure 39

t

RDP

Interval from last COLC packet with RD command to ROWR packet with

PRER.

4

4

4

-

t

CYCLE

Figure 15

t

RTP

Interval from last COLC packet with automatic retire command to ROWR

packet with PRER.

4

4

4

-

t

CYCLE

Figure 16

a.

Or equivalent PREC or PREX command. See Figure 14

.

b. This is a constraint imposed by the core, and is therefore in units of

μ

s rather than t

CYCLE

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM418RD4C | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD4D | 128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM416RD16AD | CAP ELECT 47UF 100V TG SMD |

| KM416RD16C | 15VPP 74DB 2 TERM CERAM BUZZER |

| KM416RD16D | 15VPP 86DB 2 TERM CERAM BUZZER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM418RD4C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD4D | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD8AC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD8AC(D)-RG60 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

| KM418RD8AC(D)-RK70 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128/144Mbit RDRAM 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。