- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377487 > IDT821068 (Integrated Device Technology, Inc.) OCTAL PROGRAMMABLE PCM CODEC PDF資料下載

參數(shù)資料

| 型號: | IDT821068 |

| 廠商: | Integrated Device Technology, Inc. |

| 元件分類: | Codec |

| 英文描述: | OCTAL PROGRAMMABLE PCM CODEC |

| 中文描述: | 八路可編程PCM編解碼器 |

| 文件頁數(shù): | 15/45頁 |

| 文件大小: | 589K |

| 代理商: | IDT821068 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

INDUSTRIAL TEMPERATURE RANGE

IDT821068 OCTAL PROGRAMMABLE PCM CODEC

15

CHOPPER CLOCK

IDT821068 offers two programmable chopper clock outputs:

CHCLK1 and CHCLK2. Both CHCLK1 and CHCLK2 are synchronous

to MCLK. CHCLK1 outputs signal with programmable 2-28 ms clock

cycle, while the frequency of CHCLK2 can be any of 256 kHz, 512 kHz

and 16.384 MHz. The frequency selection of chopper clocks can be

implemented by Global Command 8. The chopper clocks can be

used to drive the power supply switching regulators on SLICs.

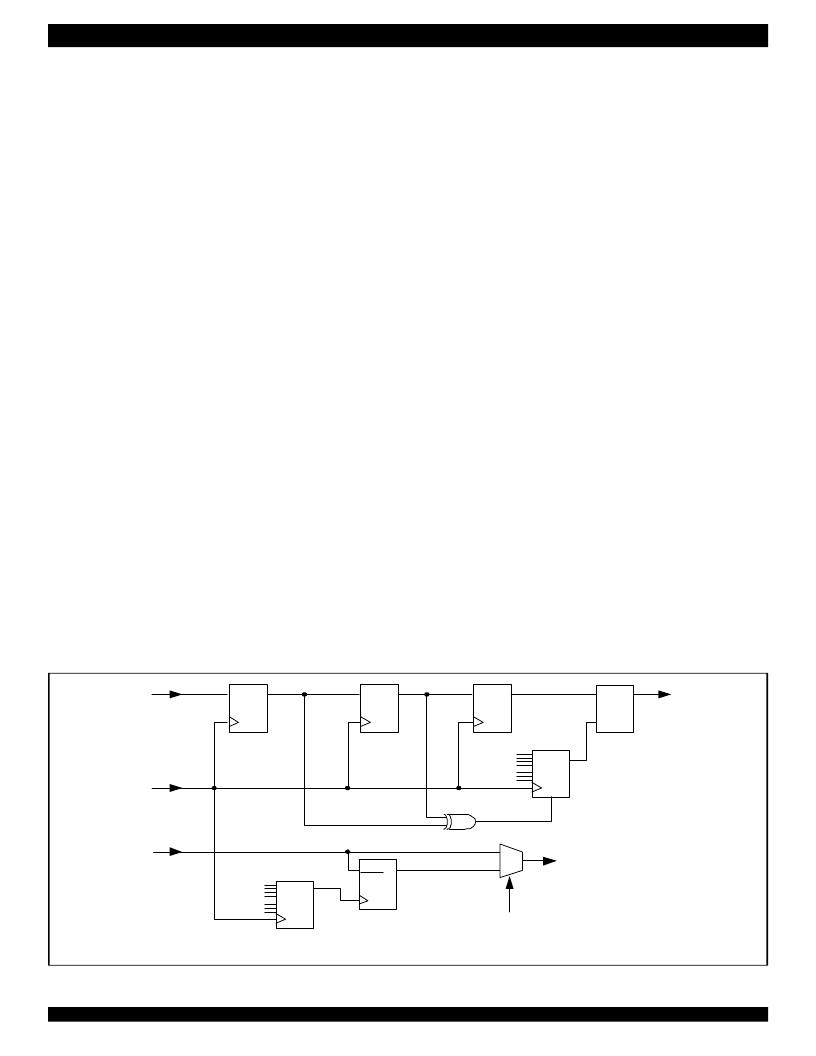

DEBOUNCE FILTERS

For each channel, IDT821068 provides two debounce filter circuits:

Debounced Switch Hook (DSH) Filter for SI1 and Ground Key (GK)

Filter for SI2 as shown in Figure 10. They are used to buffer the input

signals on SI1 and SI2 pins before changing the state of the SLIC

Debounced Input SI1/SI2 Registers (Global Command 9 and 10), or,

before changing the state of the GCI upstream C/I octet. Frame Sync

(FS) is necessary for both DSH filter and GK filter.

DSH Debounce bits in Local Command 4 can program the

debounce time of SI1 input from SLIC on individual channel. The DSH

filter is initially clocked at half of the frame sync rate (250

μ

s), and any

data changing at this sample rate resets a programmable counter.

The counter clocks at the rate of 2 ms, and the count value can be

varied from 0 to 30 which is determined by Local Command 4. The

corresponding SIA bit in the SLIC Debounced Input SI1 Register

(accessed by Global Command 9), and the corresponding channel’s

SI1 bit in GCI upstream C/I octet would not be updated with the SI1

input state until the count value is reached. SI1 bit usually contains

SLIC switch hook status.

GK Debounce bits in Local Command 4 can program the

debounce interval of SI2 input from SLIC on corresponding channel.

The debounced signal will be output to SIB of SLIC Debounced Input

SI2 Register (accessed by Global Command 10) and the

corresponding channel’s SI2 bit in GCI upstream C/I octet. The GK

debounce filter consists of an up/down counter that ranges between 0

and 6. This six-state counter is clocked by the GK timer at the

sampling period of 0-30 ms, as programmed by Local Command 4.

When the sampled value is low, the counter is decremented by each

Figure 10. Debounce Filters

D

Q

D

Q

D

Q

D

Q

E

D

Q

DSH3-DSH0

Debounce

Period

(0-30ms)

D

Q

GK3-GK0

Debounce

Interval

(0-30ms)

up/

6 states

Up/down

Counter

7 bit Debounce

Counter

7 bit Debounce

Counter

= 0

1

0

GK

SIB

SIA

SI1

4kHz

SI2

RST

FS/2

clock pulse. When the sampled value is high, the counter is

incremented by each clock pulse. When the counter increments to 6,

it sets a latch whose output is routed to the corresponding SIB bit and

GCI upstream C/I octet SI2 bit. If the counter decrements to 0, this latch

is cleared and the output bit is set to 0. In other cases, the latch, the

SIB status and the SI2 bit in GCI upstream C/I octet remain in their

previous state without being changed. In this way, at least six

consecutive GK clocks with the debounce input remaining at the same

state to effect an output change.

DUAL TONE AND RING GENERATION

Each channel of IDT821068 has two tone generators, Tone 0

generator and Tone1 generator, which can produce a gain-adjustable

dual tone signal and output it on VOUT pin. The dual tone signal can

be used for the signal generations such as test, DTMF, dial tone, busy

tone, congestion tone and Caller-ID Alerting Tone etc.

The Tone0 generator and Tone1 generator of each channel can be

enabled or disabled independently by setting the T0E and T1E bits in

Local Command 6. The frequency of the tones generated can be

programmed from 1 Hz to 4.095 kHz with 4095 steps. Local

Command 5 provides 12 bits for each tone generator to set the

frequency.

The gain of the Tone0 and Tone1 signal of each channel is

programmed by the TG[5:0] bits in Local Command 6, in the range of

-3 dB to -39 dB. The gain of each tone can calculated by the formula

below:

G = 20 × lg (Tg×2/256) + 3.14

where, Tg is the decimal value of TG[5:0].

The Dual Tone Output Invert bit (TOI) of Global Command 19 can

invert the output tone signal. When it is ‘0’, it means no inversion;

when it is ‘1’, the output tone signal will be inverted.

Ring signal is a special signal generated by the dual tone

generators. When only one tone generator is enabled or both tone

generators produce the same tone, and frequency of the tone is set as

ring signal required (10 Hz to 100 Hz), the VOUT pin will output the

Ring signal.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT821068PX | OCTAL PROGRAMMABLE PCM CODEC |

| IDT821621 | LONG HAUL SLIC |

| IDT821621J | LONG HAUL SLIC |

| IDT82P2281 | Single T1/E1/J1 Long Haul Short Haul Transceiver |

| IDT82P2281PN | Single T1/E1/J1 Long Haul Short Haul Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT821068PX | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:OCTAL PROGRAMMABLE PCM CODEC |

| IDT821621 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:LONG HAUL SLIC |

| IDT821621J | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:LONG HAUL SLIC |

| IDT8217LP35P | 制造商:Integrated Device Technology Inc 功能描述: |

| IDT82ALVCH16823PA | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:3.3V CMOS 18-BIT BUS-INTERFACE FLIPFLOP WITH 3-STATE OUTPUTS AND BUS-HOLD |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。