- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379208 > ICY7C1362C-166BGXI (CYPRESS SEMICONDUCTOR CORP) 9-Mbit (256K x 36/512K x 18) Pipelined SRAM PDF資料下載

參數(shù)資料

| 型號: | ICY7C1362C-166BGXI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 9-Mbit (256K x 36/512K x 18) Pipelined SRAM |

| 中文描述: | 512K X 18 CACHE SRAM, 3.5 ns, PBGA119 |

| 封裝: | 14 X 22 MM, 2.40 MM HEIGHT, LEAD FREE, PLASTIC, BGA-119 |

| 文件頁數(shù): | 9/31頁 |

| 文件大?。?/td> | 432K |

| 代理商: | ICY7C1362C-166BGXI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

PRELIMINARY

CY7C1360C

CY7C1362C

Document #: 38-05540 Rev. *C

Page 9 of 31

Because the CY7C1360C/CY7C1362C is a common I/O

device, the Output Enable (OE) must be deasserted HIGH

before presenting data to the DQs inputs. Doing so will

three-state the output drivers. As a safety precaution, DQs are

automatically three-stated whenever a Write cycle is detected,

regardless of the state of OE.

Burst Sequences

The CY7C1360C/CY7C1362C provides a two-bit wraparound

counter, fed by A

1

, A

0

, that implements either an interleaved

or linear burst sequence. The interleaved burst sequence is

designed specifically to support Intel Pentium applications.

The linear burst sequence is designed to support processors

that follow a linear burst sequence. The burst sequence is user

selectable through the MODE input.

Asserting ADV LOW at clock rise will automatically increment

the burst counter to the next address in the burst sequence.

Both Read and Write burst operations are supported.

Sleep Mode

The ZZ input pin is an asynchronous input. Asserting ZZ

places the SRAM in a power conservation “sleep” mode. Two

clock cycles are required to enter into or exit from this “sleep”

mode. While in this mode, data integrity is guaranteed.

Accesses pending when entering the “sleep” mode are not

considered valid nor is the completion of the operation

guaranteed. The device must be deselected prior to entering

the “sleep” mode. CE

1

, CE

2

, CE

3[2]

, ADSP, and ADSC must

remain inactive for the duration of t

ZZREC

after the ZZ input

returns LOW.

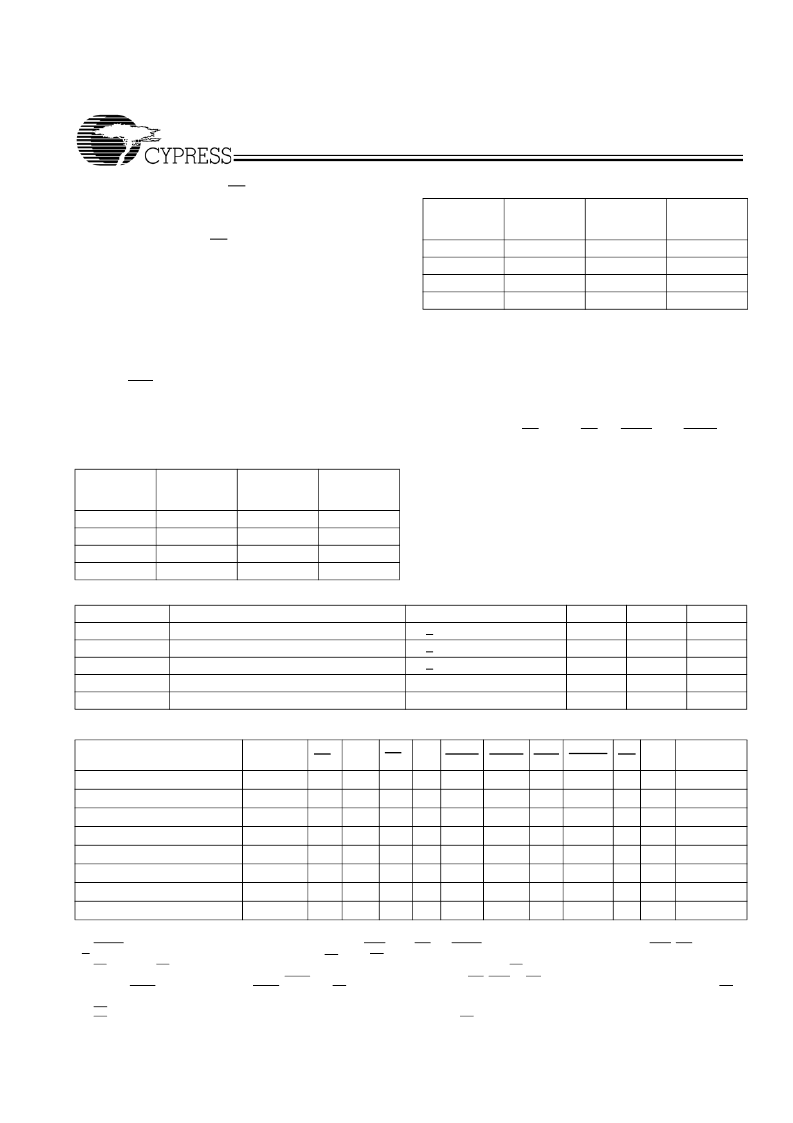

Interleaved Burst Address Table

(MODE = Floating or V

DD

)

First

Address

A

1

, A

0

A

1

, A

0

00

01

10

11

ZZ Mode Electrical Characteristics

Second

Address

Third

Address

A

1

, A

0

10

11

00

01

Fourth

Address

A

1

, A

0

11

10

01

00

01

00

11

10

Linear Burst Address Table (MODE = GND)

First

Address

A

1

, A

0

00

01

10

11

Second

Address

A

1

, A

0

01

10

11

00

Third

Address

A

1

, A

0

10

11

00

01

Fourth

Address

A

1

, A

0

11

00

01

10

Parameter

I

DDZZ

t

ZZS

t

ZZREC

t

ZZI

t

RZZI

Description

Test Conditions

ZZ > V

DD

– 0.2V

ZZ > V

DD

– 0.2V

ZZ < 0.2V

This parameter is sampled

This parameter is sampled

Min.

Max.

50

2t

CYC

Unit

mA

ns

ns

ns

ns

Sleep mode standby current

Device operation to ZZ

ZZ recovery time

ZZ Active to sleep current

ZZ Inactive to exit sleep current

2t

CYC

2t

CYC

0

Truth Table

[3, 4, 5, 6, 7, 8]

Operation

Address

Used

None

None

None

None

None

None

External

External

CE

1

H

L

L

L

L

X

L

L

CE

2

X

L

X

L

X

X

H

H

CE

3

X

X

H

X

H

X

L

L

ZZ

L

L

L

L

L

H

L

L

ADSP ADSC ADV WRITE

X

L

L

X

L

X

H

L

H

L

X

X

L

X

L

X

OE CLK

X

X

X

X

X

X

L

H

DQ

Deselect Cycle, Power Down

Deselect Cycle, Power Down

Deselect Cycle, Power Down

Deselect Cycle, Power Down

Deselect Cycle, Power Down

Sleep Mode, Power Down

READ Cycle, Begin Burst

READ Cycle, Begin Burst

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

L-H

L-H

L-H

L-H

L-H

X

L-H

L-H

Three-State

Three-State

Three-State

Three-State

Three-State

Three-State

Q

Three-State

Notes:

3. X = “Don't Care.” H = Logic HIGH, L = Logic LOW.

4. WRITE = L when any one or more Byte Write Enable signals and BWE = L or GW = L. WRITE = H when all Byte Write Enable signals, BWE, GW = H.

5. The DQ pins are controlled by the current cycle and the OE signal. OE is asynchronous and is not sampled with the clock.

6. CE

1

, CE

2

, and CE

3

are available only in the TQFP package. BGA package has only two chip selects CE

1

and CE

2

.

7. The SRAM always initiates a read cycle when ADSP is asserted, regardless of the state of GW, BWE, or BW

. Writes may occur only on subsequent clocks

after the ADSP or with the assertion of ADSC. As a result, OE must be driven HIGH prior to the start of the Write cycle to allow the outputs to three-state. OE is

a don't care for the remainder of the Write cycle

8. OE is asynchronous and is not sampled with the clock rise. It is masked internally during Write cycles. During a Read cycle all data bits are Three-State when

OE is inactive or when the device is deselected, and all data bits behave as output when OE is active (LOW).

相關PDF資料 |

PDF描述 |

|---|---|

| ID100 | MONOLITHIC DUAL PICO AMPERE DIODES |

| ID100 | SCRs .5 Amp, Planar |

| IDT101494S7C | HIGH-SPEED BiCMOS ECL STATIC RAM 64K (16K】4-BIT) SRAM |

| IDT100494 | HIGH-SPEED BiCMOS ECL STATIC RAM 64K (16K】4-BIT) SRAM |

| IDT100494S10C | HIGH-SPEED BiCMOS ECL STATIC RAM 64K (16K】4-BIT) SRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ICY7C1362C-166BZI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:9-Mbit (256K x 36/512K x 18) Pipelined SRAM |

| ICY7C1367B-166BGI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:9-Mb (256K x 36/512K x 18) Pipelined DCD Sync SRAM |

| ICY7C1373C-100BGI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:18-Mbit (512K x 36/1M x 18) Flow-Through SRAM with NoBL Architecture |

| ICY7C1373D-100BGI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:18-Mbit (512K x 36/1M x 18) Flow-Through SRAM with NoBLTM Architecture |

| ICY7C1373D-100BGXI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:18-Mbit (512K x 36/1M x 18) Flow-Through SRAM with NoBLTM Architecture |

發(fā)布緊急采購,3分鐘左右您將得到回復。