- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄224000 > HYB18T1G800C4F-3 (QIMONDA AG) 128M X 8 DDR DRAM, 0.45 ns, PBGA60 PDF資料下載

參數(shù)資料

| 型號(hào): | HYB18T1G800C4F-3 |

| 廠商: | QIMONDA AG |

| 元件分類(lèi): | DRAM |

| 英文描述: | 128M X 8 DDR DRAM, 0.45 ns, PBGA60 |

| 封裝: | GREEN, PLASTIC, TFBGA-60 |

| 文件頁(yè)數(shù): | 44/58頁(yè) |

| 文件大小: | 1898K |

| 代理商: | HYB18T1G800C4F-3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)當(dāng)前第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)

HYB18T1G[40/80/16]0C4F

1-Gbit Double-Data-Rate-Two SDRAM

Internet Data Sheet

Rev. 1.01, 2008-11

49

04212008-66HT-ZLFE

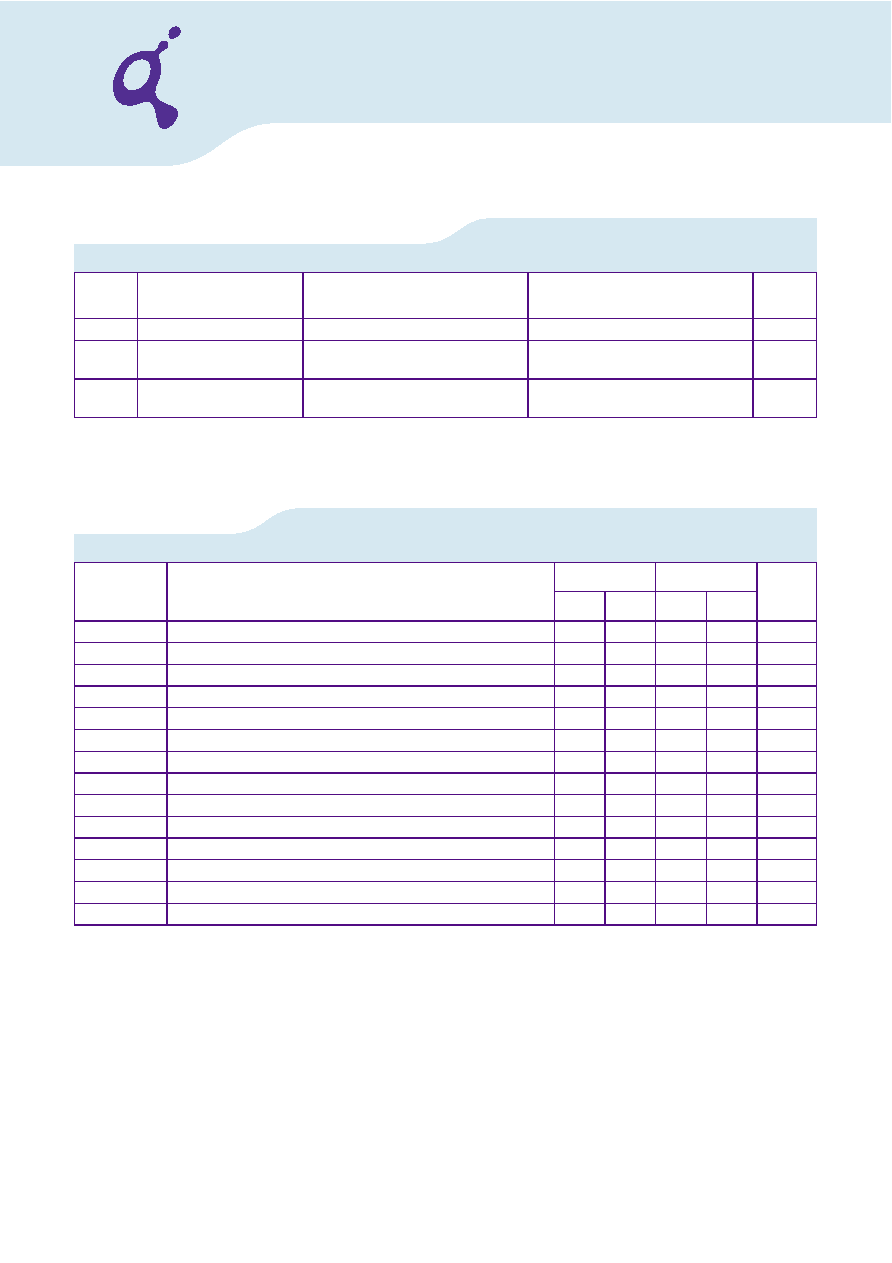

TABLE 39

Absolute Jitter Value Definitions

Example: for DDR2-667,

t

CH.ABS.MIN = (0.48 x 3000ps) – 125 ps = 1315 ps = 0.438 x 3000 ps.

Table 40 shows clock-jitter specifications.

TABLE 40

Clock-Jitter Specifications for DDR2–667 and DDR2–800

Symbol Parameter

Min.

Max.

Unit

t

CK.ABS

Clock period

t

CK.AVG(Min) + tJIT.PER(Min)

t

CK.AVG(Max) + tJIT.PER(Max)

ps

t

CH.ABS

Clock high-pulse width

t

CH.AVG(Min) x tCK.AVG(Min) + tJIT.DUTY(Min)

t

CH.AVG(Max) x tCK.AVG(Max) +

t

JIT.DUTY(Max)

ps

t

CL.ABS

Clock low-pulse width

t

CL.AVG(Min) x tCK.AVG(Min) + tJIT.DUTY(Min)

t

CL.AVG(Max) x tCK.AVG(Max) +

t

JIT.DUTY(Max)

ps

Symbol

Parameter

DDR2–667

DDR2–800

Unit

Min.

Max.

Min.

Max.

t

CK.AVG

Average clock period nominal w/o jitter

3000

8000

2500

8000

ps

t

JIT.PER

Clock-period jitter

–125

125

–100

100

ps

t

JIT(PER,LCK)

Clock-period jitter during DLL locking period

–100

100

–80

80

ps

t

JIT.CC

Cycle-to-cycle clock-period jitter

–250

250

–200

200

ps

t

JIT(CC,LCK)

Cycle-to-cycle clock-period jitter during DLL-locking period

–200

200

–160

160

ps

t

ERR.2PER

Cumulative error across 2 cycles

–175

175

–150

150

ps

t

ERR.3PER

Cumulative error across 3 cycles

–225

225

–175

175

ps

t

ERR.4PER

Cumulative error across 4 cycles

–250

250

–200

200

ps

t

ERR.5PER

Cumulative error across 5 cycles

–250

250

–200

200

ps

t

ERR(6-10PER)

Cumulative error across n cycles with n = 6 .. 10, inclusive

–350

350

–300

300

ps

t

ERR(11-50PER)

Cumulative error across n cycles with n = 11 .. 50, inclusive

–450

450

–450

450

ps

t

CH.AVG

Average high-pulse width

0.48

0.52

0.48

0.52

t

CK.AVG

t

CL.AVG

Average low-pulse width

0.48

0.52

0.48

0.52

t

CK.AVG

t

JIT.DUTY

Duty-cycle jitter

–125

125

–100

100

ps

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB3165800AJ-40 | 8M X 8 FAST PAGE DRAM, 40 ns, PDSO32 |

| HYB39S64400AT-8 | 16M X 4 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| HYC532410-50 | 4M X 32 MULTI DEVICE DRAM CARD, 50 ns, XMA88 |

| HYE18M256320CF-7.5 | 8M X 32 DDR DRAM, 6 ns, PBGA90 |

| HYM564124AR-60 | 1M X 64 EDO DRAM MODULE, DMA168 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18T256400AF-3.7 | 制造商:Infineon Technologies AG 功能描述:64M X 4 DDR DRAM, 0.5 ns, PBGA60 |

| HYB18T256400AF-5 | 制造商:Infineon Technologies AG 功能描述:SDRAM, DDR, 64M x 4, 60 Pin, Plastic, BGA |

| HYB18T256800AF-5 | 制造商:Infineon Technologies AG 功能描述: |

| HYB18T512161BF-25 | 制造商:Qimonda 功能描述:SDRAM, DDR, 32M x 16, 84 Pin, Plastic, BGA |

| HYB18T512400AF-5 | 制造商:Intersil Corporation 功能描述:SDRAM, DDR, 128M x 4, 60 Pin, Plastic, BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。