- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369679 > CYNSE70256 Network Processing PDF資料下載

參數(shù)資料

| 型號(hào): | CYNSE70256 |

| 英文描述: | Network Processing |

| 中文描述: | 網(wǎng)絡(luò)處理 |

| 文件頁(yè)數(shù): | 75/126頁(yè) |

| 文件大?。?/td> | 3302K |

| 代理商: | CYNSE70256 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)當(dāng)前第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)

CYNSE70032

Document #: 38-02042 Rev. *E

Page 75 of 126

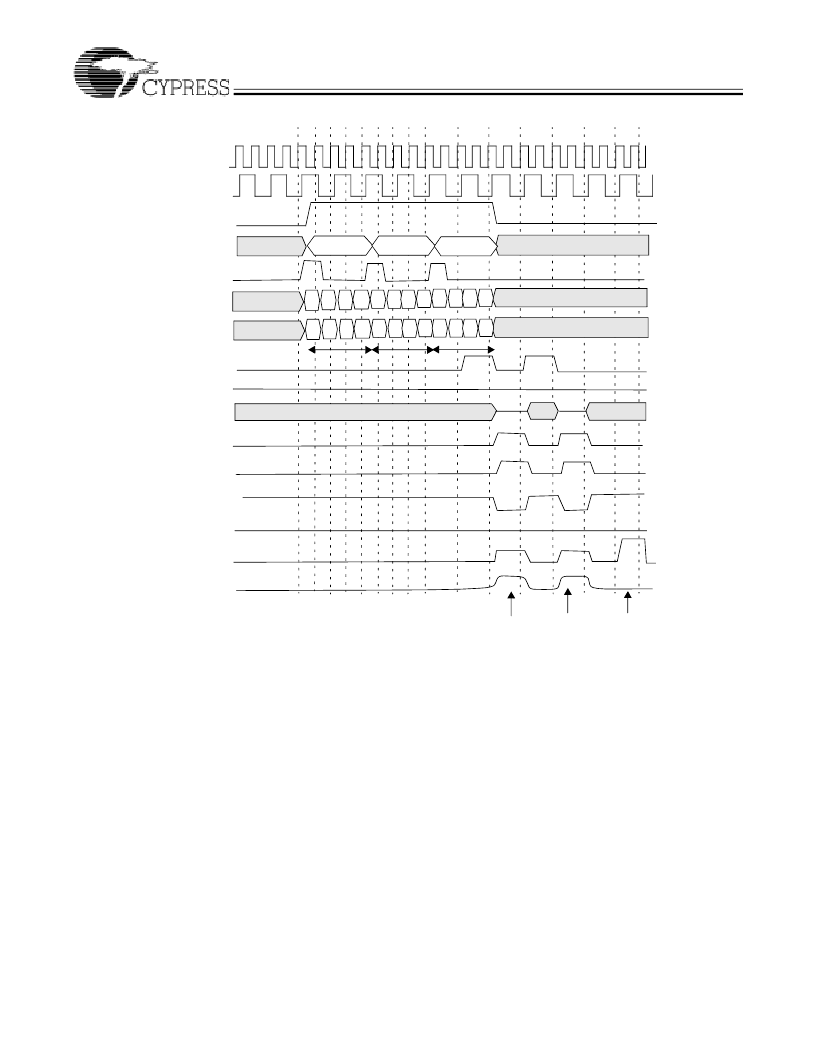

The following is the sequence of operation for a single 272-bit Search command (also see “Commands and Command Param-

eters” on page 19).

Cycle A

: The host ASIC drives CMDV high and applies Search command code (10) on CMD[1:0] signals. CMD[5:3] signals

must be driven with the index to the GMR pair used for bits [271:136] of the data being searched in this operation. DQ[67:0]

must be driven with the 68-bit data ([271:204]) to be compared against all locations 0 in the four-word 68-bit page. The CMD[2]

signal must be driven to logic 1.

Note

. CMD[2] = 1 signals that the search is a x272 bit search. CMD[8:3] in this cycle is ignored.

Cycle B

: The host ASIC continues to drive CMDV high and applies Search command code (10) on CMD[1:0]. The DQ[67:0]

is driven with the 68-bit data ([203:136]) to be compared against all locations 1 in the four 68-bits-word page.

Cycle C

: The host ASIC drives CMDV high and applies Search command code (10) on CMD[1:0] signals. CMD[5:3] signals

must be driven with the index to the GMR pair used for bits [135:0] of the data being searched. CMD[8:6] signals must be

driven with the bits that will be driven on SADR[21:19] by this device if it has a hit. DQ[67:0] must be driven with the 68-bit data

([135:68]) to be compared against all locations 2 in the four 68-bits-word page. The CMD[2] signal must be driven to logic 0.

Cycle D

: The host ASIC continues to drive CMDV high and applies Search command code (10) on CMD[1:0]. CMD[8:6] signals

must be driven with the index of the SSR that will be used for storing the address of the matching entry and the hit flag (see

page 14 for the description of SSR[0:7]). The DQ[67:0] is driven with the 68-bit data ([67:0]) to be compared to all locations 3

in the four 68-bits-word page. CMD[5:2] is ignored because the Learn instruction is not supported for ×272 tables.

Note

. For 272-bit searches, the host ASIC must supply four distinct 68-bit data words on DQ[67:0] during cycles A, B, C, and D.

The GMR index in cycle A selects a pair of GMRs in each of the eight devices that apply to DQ data in cycles A and B. The GMR

index in cycle C selects a pair of GMRs in each of the eight devices that apply to DQ data in cycles C and D.

cycle

1

CLK2X

CMDV

CE_L

OE_L

(Miss on

cycle

2

cycle

3

cycle

4

cycle

5

cycle

6

cycle

7

cycle

8

cycle

9

cycle

10

CFG = 10101010, HLAT = 000, TLSZ = 01, LRAM = 1, LDEV = 1.

Note: |(LHI[6:0]) stands for the boolean ‘OR’ of the entire bus LHI[6:0].

Note: Each bit in LHO[1:0] is the same logical signal.

PHS_L

SADR[21:0]

SSF

SSV

Search1

Search2 Search3

0

(Global

miss.)

|(LHI[6:0])

LHO[1:0]

this device.)

0

z

0

ALE_L

WE_L

1

z

1

0

z

1

0

0

z

0

CMD[1:0]

CMD[8:2]

01

01

Search1

Search2

A B A B A B A B

CMD[2]

A B C D A B C D

D1

DQ

D2

A B C D

D3

A B A B

01

Search3

z

0

0

z

z

1

z

z

0

0

z

0

Figure 13-51. Timing Diagram for 272-bit Search Device Number 7 (Last Device)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CZET101 | Clock Driver |

| CZEU101 | Quad Peripheral Driver |

| CZEZ101 | Triple Peripheral Driver |

| CZSP103 | Voltage Reference |

| CZT122 | TRANSISTOR | BJT | DARLINGTON | NPN | 100V V(BR)CEO | 5A I(C) | SOT-223 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CYNSE70256-66BGC | 制造商:Cypress Semiconductor 功能描述: |

| CYNSE70256-66BHC | 制造商:Cypress Semiconductor 功能描述:COMMUNICATIONS, NETWORK SEARCH ENGINE - Trays |

| CYONS10017-LBXC | 制造商:Cypress Semiconductor 功能描述: |

| CYONS1001G-LBXC | 制造商:Cypress Semiconductor 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| CYONS1001L | 制造商:CYPRESS 制造商全稱(chēng):Cypress Semiconductor 功能描述:OvationONS⑩ 1L - Laser Navigation Sensor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。