- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166131 > AK4665AEN SPECIALTY CONSUMER CIRCUIT, QCC32 PDF資料下載

參數(shù)資料

| 型號(hào): | AK4665AEN |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, QCC32 |

| 封裝: | 5 X 5 MM, 0.50 MM PITCH, LEAD FREE, QFN-32 |

| 文件頁(yè)數(shù): | 34/52頁(yè) |

| 文件大小: | 522K |

| 代理商: | AK4665AEN |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)當(dāng)前第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

ASAHI KASEI

[AK4665A]

MS0440-E-01

2006/05

- 4 -

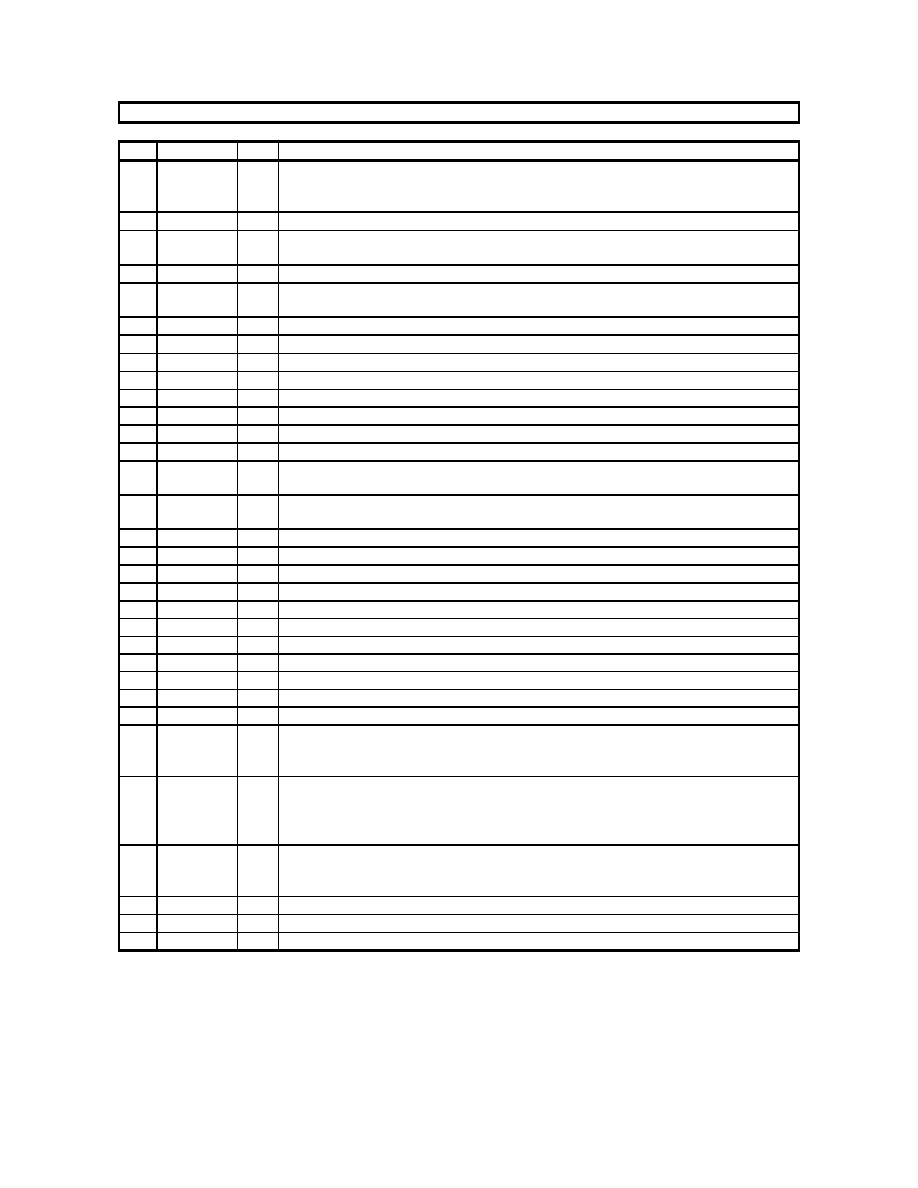

PIN/FUNCTION

No.

Pin Name

I/O

Function

1

LRCK

I

L/R Clock Pin

This clock determines which audio channel is currently being output on SDTO pin and

input on SDTI pin.

2

MCLK

I

Master Clock Input Pin

3

BICK

I

Serial Bit Clock Pin

This clock is used to latch audio data.

4

SDTI

I

Audio Data Input Pin

5

SDTO

O

Audio Data Output Pin

SDTO pin goes to DVSS when PDN pin is “L” or PMADC bit is “0”.

6

TVDD

-

Digital I/O Power Supply Pin

7

DVSS

-

Digital Ground Pin

8

DVDD

-

Digital Power Supply Pin

9

CP

O

Positive Charge Pump Capacitor Terminal Pin

10

CN

I

Negative Charge Pump Capacitor Terminal Pin

11

HVDD

-

Power Supply Pin for Headphone Amplifier and Charge Pump Circuit

12

HVSS

-

Ground Pin for Headphone Amplifier and Charge Pump Circuit

13

NVSS

O

Negative Voltage Output Pin for Headphone Amplifier and Charge Pump Circuit

14

HPL

O

Lch Headphone Amplifier Output Pin

HPL pin goes to AVSS when PMHPL bit is “0”.

15

HPR

O

Rch Headphone Amplifier Output Pin

HPR pin goes to AVSS when PMHPR bit is “0”.

16

ROUT

O

Rch Analog Output Pin

17

LOUT

O

Lch Analog Output Pin

18

MIN

I

Mono Analog Input Pin

19

RIN

I

Rch Analog Input Pin

20

LIN

I

Lch Analog Input Pin

21

AINR1

I

Rch Analog Input 1 Pin for ADC (LINE Input)

22

AINL1

I

Lch Analog Input 1 Pin for ADC (LINE Input)

23

MPWR

O

MIC Power Supply Pin

24

MICIN

I

MIC Input Pin

25

AVSS

-

Analog Ground Pin

26

AVDD

-

Analog Power Supply Pin

27

VCOM

O

Common Voltage Output Pin, 1.2V (typ, respect to AVSS)

Normally connected to AVSS pin with a 0.1

F ceramic capacitor in parallel with a

2.2

F electrolytic capacitor. VCOM pin goes to AVSS when PMVCM bit = ”0”.

28

VREF

O

Reference Voltage Output Pin, 2.1V (typ, respect to AVSS)

Normally connected to AVSS pin with a 0.1

F ceramic capacitor in parallel with a

4.7

F electrolytic capacitor. VREF pin goes to AVSS when PMVCM bit = ”0”.

29

PDN

I

Power-down Pin

When “L”, the AK4665A is in power-down mode and is held in reset. The AK4665A

should always be reset upon power-up.

30

CSN

I

Control Data Chip Select Pin

31

CCLK

I

Control Clock Input Pin

32

CDTI

I

Control Data Input Pin

Note 1. Do not allow digital input pins except analog input pins (MICIN, AINL1, AINR1, LIN, RIN and MIN pins) to

float.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AK5368192WP-80 | 8M X 36 FAST PAGE DRAM MODULE, 80 ns, SMA72 |

| AK5385A | 24BIT 192KHZ ADC |

| AK8406A | AK8406A |

| AK8432 | 6CH 10bit 40MSPS】3 |

| AK8850 | NTSC Digital Video Decoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AK4666VQ | 功能描述:IC CODEC STEREO 20BIT LQFP 制造商:akm semiconductor inc. 系列:* 零件狀態(tài):上次購(gòu)買時(shí)間 標(biāo)準(zhǔn)包裝:1,000 |

| AK4671 | 制造商:AKM 制造商全稱:AKM 功能描述:Stereo CODEC with MIC/RCV/HP-AMP |

| AK4671_10 | 制造商:AKM 制造商全稱:AKM 功能描述:Stereo CODEC with MIC/RCV/HP-AMP |

| AK4671EG | 制造商:AKM 制造商全稱:AKM 功能描述:Stereo CODEC with MIC/RCV/HP-AMP |

| AK4673 | 制造商:AKM 制造商全稱:AKM 功能描述:Stereo CODEC with MIC/HP-AMP and Touch Screen Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。