- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4430 > A1020B-1VQ80C (Microsemi SoC)IC FPGA 2K GATES 80-VQFP COM PDF資料下載

參數(shù)資料

| 型號(hào): | A1020B-1VQ80C |

| 廠商: | Microsemi SoC |

| 文件頁(yè)數(shù): | 2/98頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 2K GATES 80-VQFP COM |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | ACT™ 1 |

| LAB/CLB數(shù): | 547 |

| 輸入/輸出數(shù): | 69 |

| 門(mén)數(shù): | 2000 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 80-TQFP |

| 供應(yīng)商設(shè)備封裝: | 80-VQFP(14x14) |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)

10

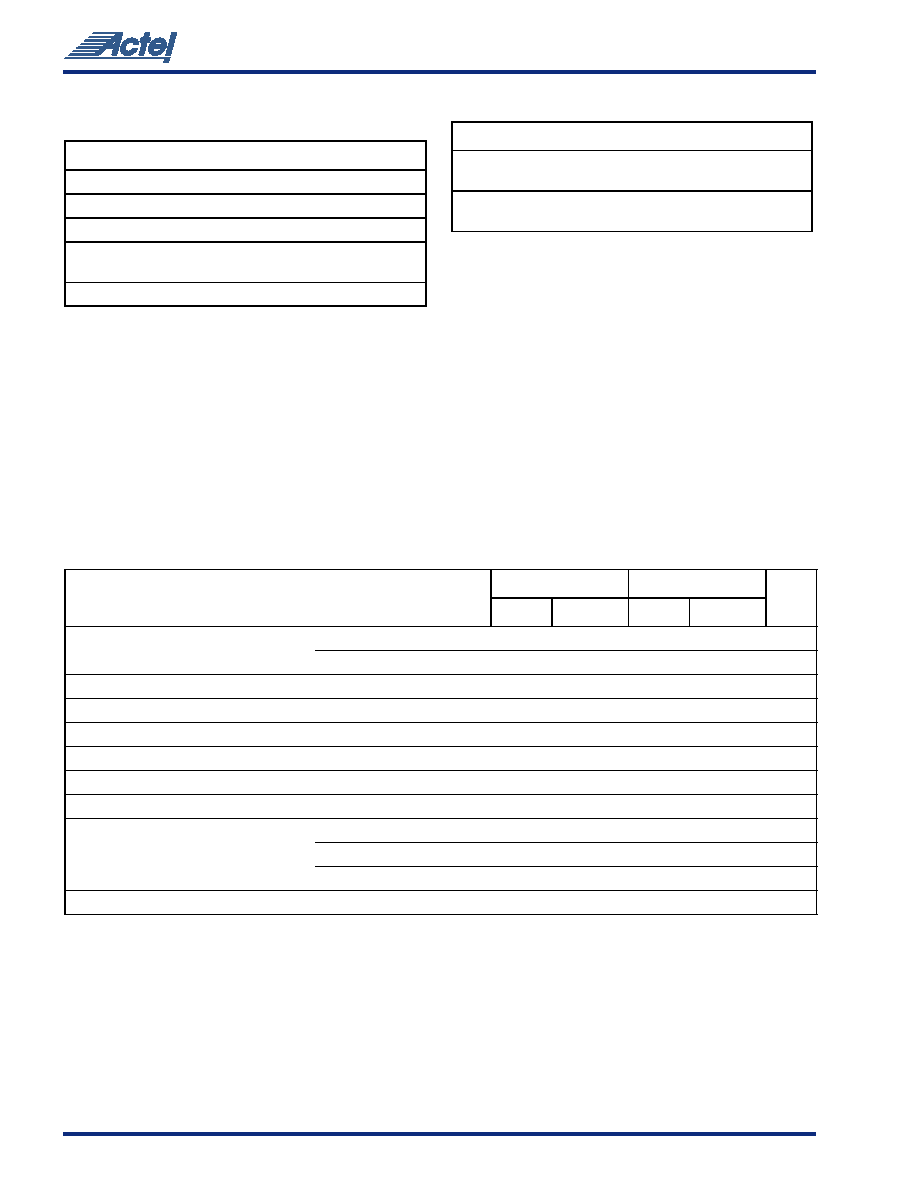

Ab s o l u t e Ma x i mu m R a t i n g s 1

Free air temperature range

Notes:

1.

Stresses beyond those listed under “Absolute Maximum Ratings”

may cause permanent damage to the device. Exposure to

absolute maximum rated conditions for extended periods may

affect device reliability. Devices should not be operated outside

the recommended operating conditions.

2.

VPP = VCC , except during device programming.

3.

VSV = VCC , except during device programming.

4.

VKS = GND , except during device programming.

5.

Device inputs are normally high impedance and draw extremely

low current. However, when input voltage is greater than VCC +

0.5V or less than GND – 0.5V, the internal protection diode will be

forward biased and can draw excessive current.

Re com m e nde d Op er at i n g Co ndi t i on s

Notes:

1.

Ambient temperature (TA) is used for commercial and

industrial; case temperature (TC) is used for military.

2.

All power supplies must be in the recommended operating range.

For more information, refer to the Power-Up Design Considerations

application note at http://www.actel.com/appnotes.

E l e c tric a l S p e c ific a t io n s

Notes:

1.

Actel devices can drive and receive either CMOS or TTL signal levels. No assignment of I/Os as TTL or CMOS is required.

2.

Tested one output at a time, VCC = min.

3.

Not tested; for information only.

4.

VOUT = 0V, f = 1 MHz

Symbol

Parameter

Limits

Units

VCC

DC Supply Voltage2, 3, 4

–0.5 to +7.0

V

VI

Input Voltage

–0.5 to VCC +0.5

V

VO

Output Voltage

–0.5 to VCC +0.5

V

IIO

I/O Source Sink

Current5

±20

mA

TSTG

Storage Temperature

–65 to +150

°C

Parameter

Commercial

Military

Units

Temperature

Range1

0 to +70

–55 to +125

°C

Power Supply

Tolerance2

±5

±10

%VCC

Symbol

Parameter

Test Condition

Commercial

Military

Units

Min.

Max.

Min.

Max.

VOH

1, 2

HIGH Level Output

IOH = –4 mA (CMOS)

3.7

V

IOH = –6 mA (CMOS)

3.84

V

VOL

1, 2

LOW Level Output

IOL = +6 mA (CMOS)

0.33

0.4

V

VIH

HIGH Level Input

TTL Inputs

2.0

VCC + 0.3

2.0

VCC + 0.3

V

VIL

LOW Level Input

TTL Inputs

–0.3

0.8

–0.3

0.8

V

IIN

Input Leakage

VI = VCC or GND

–10

+10

–10

+10

A

IOZ

3-state Output Leakage

VO = VCC or GND

–10

+10

–10

+10

A

CIO

I/O Capacitance3, 4

10

pF

ICC(S)

Standby VCC Supply Current VI = VCC or GND, IO = 0 mA

ACT 1

3

20

mA

ACT 2/3/1200XL/3200DX

2

20

mA

ICC(D)

Dynamic VCC Supply Current

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A10V20B-VQ80C | IC FPGA 2K GATES 80-VQFP COM |

| A1020B-1VQG80C | IC FPGA 2K GATES 80-VQFP COM |

| FMC17DRYI-S734 | CONN EDGECARD 34POS DIP .100 SLD |

| ESC65DRYS-S734 | CONN EDGECARD 130PS DIP .100 SLD |

| RSC31DTES | CONN EDGECARD 62POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A1020B-1VQ80I | 功能描述:IC FPGA 2K GATES 80-VQFP IND RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:ACT™ 1 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A1020B-1VQ84B | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:ACT 1 Series FPGAs |

| A1020B-1VQ84C | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:ACT 1 Series FPGAs |

| A1020B-1VQ84I | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:ACT 1 Series FPGAs |

| A1020B-1VQ84M | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:ACT 1 Series FPGAs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。