- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24828 > 935268252551 (NXP SEMICONDUCTORS) 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP144 PDF資料下載

參數(shù)資料

| 型號(hào): | 935268252551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP144 |

| 封裝: | 20 X 20 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-486-1, LQFP-144 |

| 文件頁數(shù): | 67/80頁 |

| 文件大小: | 306K |

| 代理商: | 935268252551 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當(dāng)前第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Philips Semiconductors

Preliminary specification

PDI1394L40

1394 enhanced AV link layer controller

2000 Dec 15

4

8.0

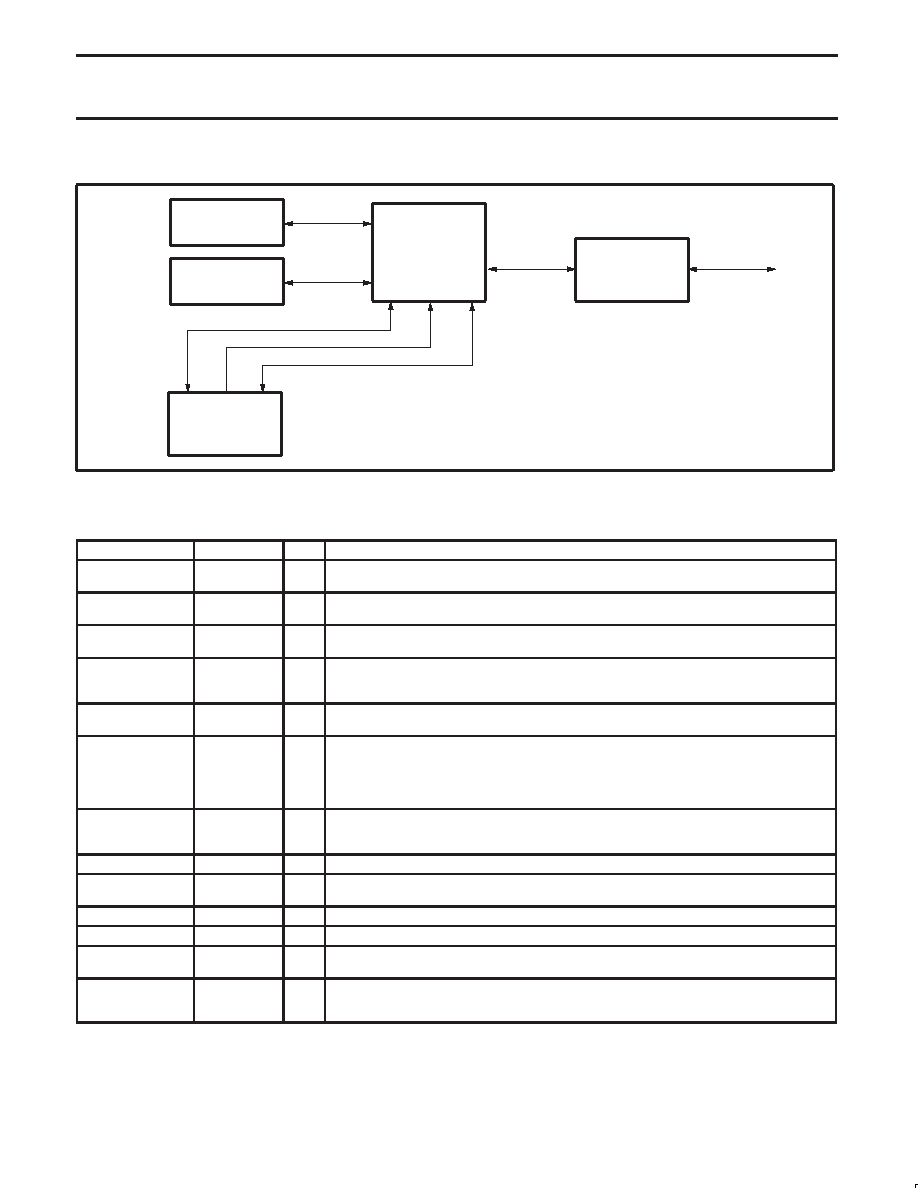

APPLICATION DIAGRAM

MPEG OR DVC

DECODER

PDI1394L40

AV LINK

AV

INTERFACE

PDI1394Pxx

PHY

PHY–LINK

INTERFACE

HOST CONTROLLER

DATA 16/

ADDRESS 9/

INTERRUPT & CONTROL

1394 CABLE

INTERFACE

MPEG OR DVC

DECODER

AV

INTERFACE

SV01835

9.0

PIN DESCRIPTION

9.1

Host Interface

PIN No.

PIN SYMBOL

I/O

NAME AND FUNCTION

13, 14, 15, 16, 19,

20, 21, 22

HIF AD[7:0]

I/O

Host Interface Data 7 (MSB) through 0. Byte wide data path to internal registers.

1, 2, 3, 4, 7, 8, 9,

10

HIF D[15:8]

I/O

Host Interface Data 15 (MSB) through 8. Only used in 16 bit access mode (HIF

16BIT = HIGH).

26, 27, 28, 29, 30,

31, 32, 33

HIF A[7:0]

I/O

Host Interface Address 0 through 8. Provides the host with a byte wide interface to internal

registers. See description of Host Interface for addressing rules (Section 12.5).

25

HIF A8

I

Control bit used to indicate the first byte/word of a read function or the last byte/word of a write

function so that the data quadlet is fetched or stored. See Section 12.5 for more information

regarding the host interface.

36

HIF CSN

I

Chip Select (active LOW). Host bus control signal to enable access to the FIFO and control

and status registers.

37

HIF WRN

I

Write enable. When asserted (LOW) in conjunction with HIF CSN, a write to the PDI1394L40

internal registers is requested. (NOTE: HIF WRN and HIF RDN : if these are both LOW in

conjunction with HIF CSN, then a write cycle takes place. This can be used to connect CPUs

that use R/W_N line rather than separate RD_N and WR_N lines. In that case, connect the

R/W_N line to the HIF WRN and tie HIF RDN LOW.)

38

HIF INTN

O

Interrupt (active LOW). Indicates a interrupt internal to the PDI1394L40. Read the General

Interrupt Register for more information. This pin is open drain and requires a 1K

W pull-up

resistor.

39

HIF ALE

I

Address latch enable. Used in multiplex mode only.

40

HIF RDN

I

Read enable. When asserted (LOW) in conjunction with HIF CSN, a read of the PDI1394L40

internal registers is requested.

41

HIF WAIT

O

Wait signal. Signals Host interface in WAIT condition when HI. See Section 12.5.

42

RESETN

I

Reset (active LOW). The asynchronous master reset to the PDI1394L40.

45

HIF 16BIT

I

Host interface mode pin. When LOW HIF operates in 8 bit mode. When HIGH HIF operates in

16 bit mode.

46

HIF MUX

I

Host interface mode pin. When LOW HIF operates in non-multiplex mode, when HIGH HIF

operates in multiplex mode. When HIGH, the low-order eight address bits are multiplexed with

data on HIF AD[7:0], otherwise they are non-multiplexed and supplied on A[7:0].

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 08008GOC | 125 A, 800 V, SCR, TO-209AC |

| 08008GOD | 125 A, 800 V, SCR, TO-208AD |

| 08010GOB | 125 A, 1000 V, SCR, TO-209AC |

| 08010GOC | 125 A, 1000 V, SCR, TO-209AC |

| 08010GOD | 125 A, 1000 V, SCR, TO-208AD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。