- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24828 > 935268252551 (NXP SEMICONDUCTORS) 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP144 PDF資料下載

參數(shù)資料

| 型號: | 935268252551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP144 |

| 封裝: | 20 X 20 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-486-1, LQFP-144 |

| 文件頁數(shù): | 37/80頁 |

| 文件大?。?/td> | 306K |

| 代理商: | 935268252551 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Philips Semiconductors

Preliminary specification

PDI1394L40

1394 enhanced AV link layer controller

2000 Dec 15

39

12.6.2.13

Link data confirmation formats

After a request, response, or asynchronous stream packet is transmitted, the asynchronous transmitter assembles a Link data confirmation (see

Figure 32) which is used to confirm the transmission to the higher layers. Packets transmitted from the Transmit Request FIFO are confirmed by

a confirmation written into the Receive Request FIFO and packets transmitted from the Transmit Response FIFO are confirmed by a

confirmation written into the Receive Response FIFO.

Outgoing packets and their confirmations are associated by their tLabels. It is the user’s responsibility to assure the uniqueness of active

tLabels.

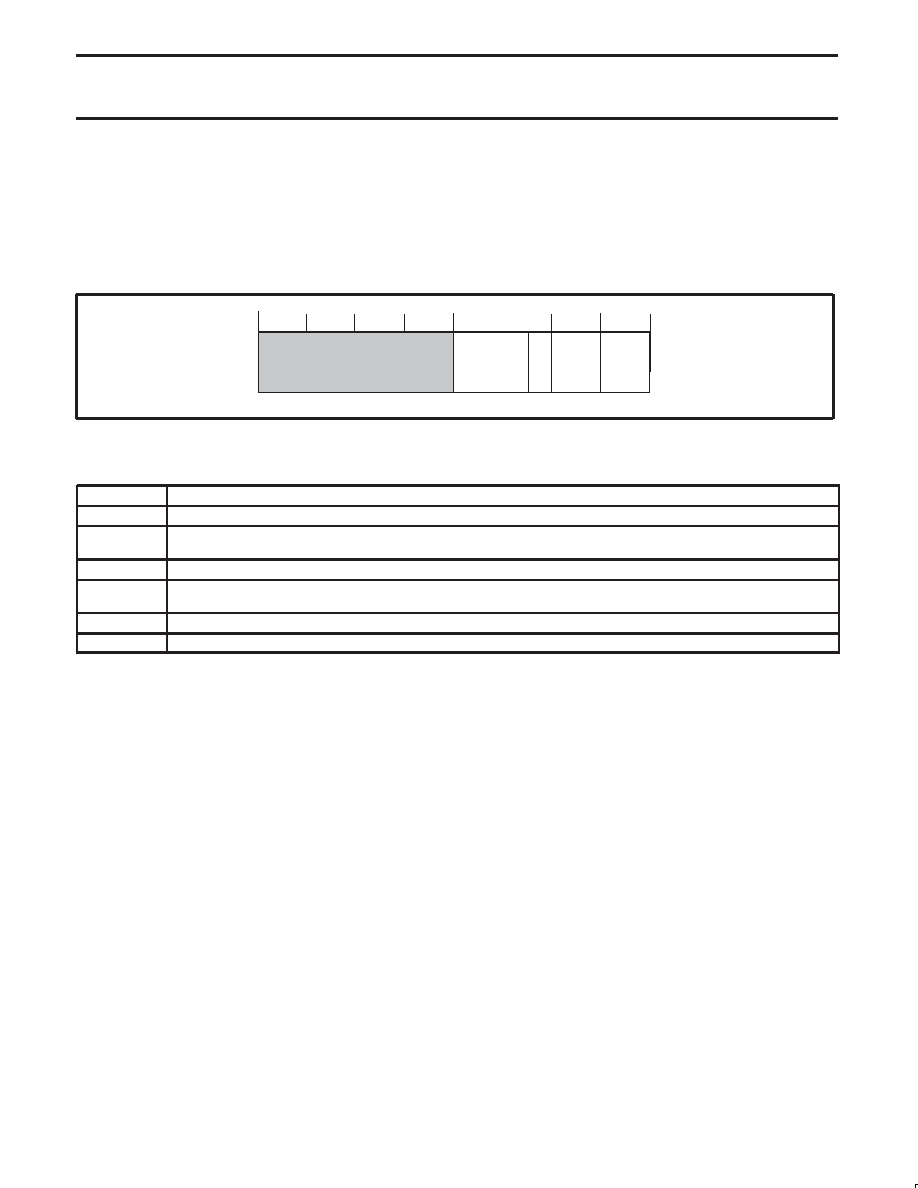

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

conf

tLabel

3130

1000

01

SV01051

Figure 32.

Request and response confirmation format

Table 5.

Confirmation codes

CODE1

DESCRIPTION

0

Non-broadcast packet transmitted; addressed node returned no acknowledge (transaction complete).

1

Broadcast packet transmitted or non-broadcast packet transmitted; addressed node returned an acknowledge complete

(transaction complete).

2

Non-broadcast packet transmitted; addressed node returned an acknowledge pending.

4

Retry limit exceeded; destination node hasn’t accepted the non-broadcast packet within the maximum number of retries

(transaction complete).

D16

Acknowledge data error received (transaction complete).

E16

Acknowledge type error received (transaction complete).

NOTE:

1. All other codes are reserved.

12.7

Interrupts

The PDI1394L40 provides a single interrupt line (HIF INTN) for connection to a host controller. Status indications from five major areas of the

device are collected and ORed together to activate HIF INTN. Status from four major areas of the device are collected in five status registers;

LNKPHYINTACK, ITXINTACK, IRXINTACK, ASYINTACK and RDI. At this level, each individual status can be enabled to generate a chip-level

interrupt by activating HIF INTN. To aid in determining the source of a chip-level interrupt, the major area of the device generating an interrupt is

indicated in the lower 4 bits of the GLOBCSR register. These bits are non-latching Read-Only status bits and do not need to be acknowledged.

To acknowledge and clear a standing interrupt, the bit in LNKPHYINTACK, ITXINTACK, IRXINTACK, ASYINTACK or RDI causing the interrupt

status has to be written to a logic ‘1’; Note: Writing a value of ‘0’ to the bit has no effect.

12.7.1

Determining and Clearing Interrupts

When responding to an interrupt event generated by the PDI1394L40, or operating in polled mode, the first register examined is the RDI

register. Since the addition of the RDI register (at 0x0b0), it will be necessary to first interrogate the RDI register independent of the GLOBCSR

register in order to locate the source of an interrupt. Embedded software should be built to perform this function. It is recommended that this

interrogation take place BEFORE the read of the GLOBCSR register is accomplished. The reason for this added step stems from the fact that

none of the other link registers can be accurately read if the link is in power–down mode. If an attempt to read the GLOBCSR is made during

link power–down, a quadlet will be read, but the quadlet data will not be the contents of the GLOBCSR. Once it has been determined that the

interrupt was not a result of a bit setting in the RDI register, the GLOBCSR register should be tested next. The least significant nibble contains

interrupt status bits from general sections of the device; the link layer controller, the AV transmitter, the AV receiver, and the asynchronous

transceiver. The bits in GLOBCSR[3:0] are self clearing status bits. They represent the logical OR of all the enabled interrupt status bits in their

section of the AV Link Layer Controller.

Once an interrupt, or status is detected in GLOBCSR, the appropriate interrupt status register needs to be read, see the Interrupt Hierarchy

diagram for more detail. After all the interrupt indications are dealt with in the appropriate interrupt status register, the interrupt status indication

will automatically clear in the GLOBCSR.

All interrupt status bits in the various interrupt status registers are latching unless otherwise noted.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 08008GOC | 125 A, 800 V, SCR, TO-209AC |

| 08008GOD | 125 A, 800 V, SCR, TO-208AD |

| 08010GOB | 125 A, 1000 V, SCR, TO-209AC |

| 08010GOC | 125 A, 1000 V, SCR, TO-209AC |

| 08010GOD | 125 A, 1000 V, SCR, TO-208AD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。