- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄293971 > 5962R0150202VYX 16-BIT, 16 MHz, RISC PROCESSOR, QFP132 PDF資料下載

參數(shù)資料

| 型號: | 5962R0150202VYX |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, 16 MHz, RISC PROCESSOR, QFP132 |

| 封裝: | FP-132 |

| 文件頁數(shù): | 5/53頁 |

| 文件大?。?/td> | 458K |

| 代理商: | 5962R0150202VYX |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

13

The next three RISC address bits (RA16-RA18) are user-

definable discrete outputs. These outputs are defined as:

RA16/OD3

DMA enable (DMAEN)

RA17/OD2

power-up (GOOD)

RA18/OD1

start-up ROM enable (SUREN)

After reset these signals will be in the following states:

RA16

1, RA17

0, RA18

0.

When the UT1750AR operates in the MIL-STD-1750 mode, it

generates an address on the Operand address bus for the next

1750 instruction. If the UT1750AR has just been initialized or

has just been reset, the first memory location placed on the

Operand Address Bus is 0000H; this instruction is the first one

fetched from the 1750 memory. After this instruction is fetched

and entered into the UT1750AR, the UT1750AR uses the

opcode to “map” or point to a specific address in the RISC

memory. Since the RISC PROM programming provides 1750

emulation capability, this address in RISC memory contains a

specific RISC-coded macro allowing the UT1750AR to perform

the requisite 1750 function.

When the UT1750AR begins executing this RISC macro for

1750 emulation, the UT1750AR begins to operate as if it were

in the RISC mode (see the previous section on RISC mode of

operation). The processor cycles of all the RISC instructions

that make up the particular macro are executed as if the

UT1750AR were operating purely as a RISC.

During RISC macro execution for the MIL-STD-1750

instruction, the internal registers of the UT1750AR hold the

intermediate results from the execution of the RISC instructions.

When the macro is complete, the UT1750AR’s registers contain

the data the MIL-STD-1750A instruction requires.

If the UT1750AR receives an interrupt during RISC macro

execution, the RISC macro completes execution before the

UT1750AR recognizes the interrupt. This is similar to

completing a single 1750 instruction rather than allowing its

interruption. The only exception is with the multiple-word

MOV 1750 instruction. For this instruction, the UT1750AR

interrupts macro execution after transferring the current word.

After the RISC macro is complete, all the UT1750AR’s internal

registers, including the status registers and/or memory locations,

contain the results of the MIL-STD-1750A instruction that has

just completed execution. The UT1750AR now fetches the next

1750 instruction from Operand memory and the process repeats.

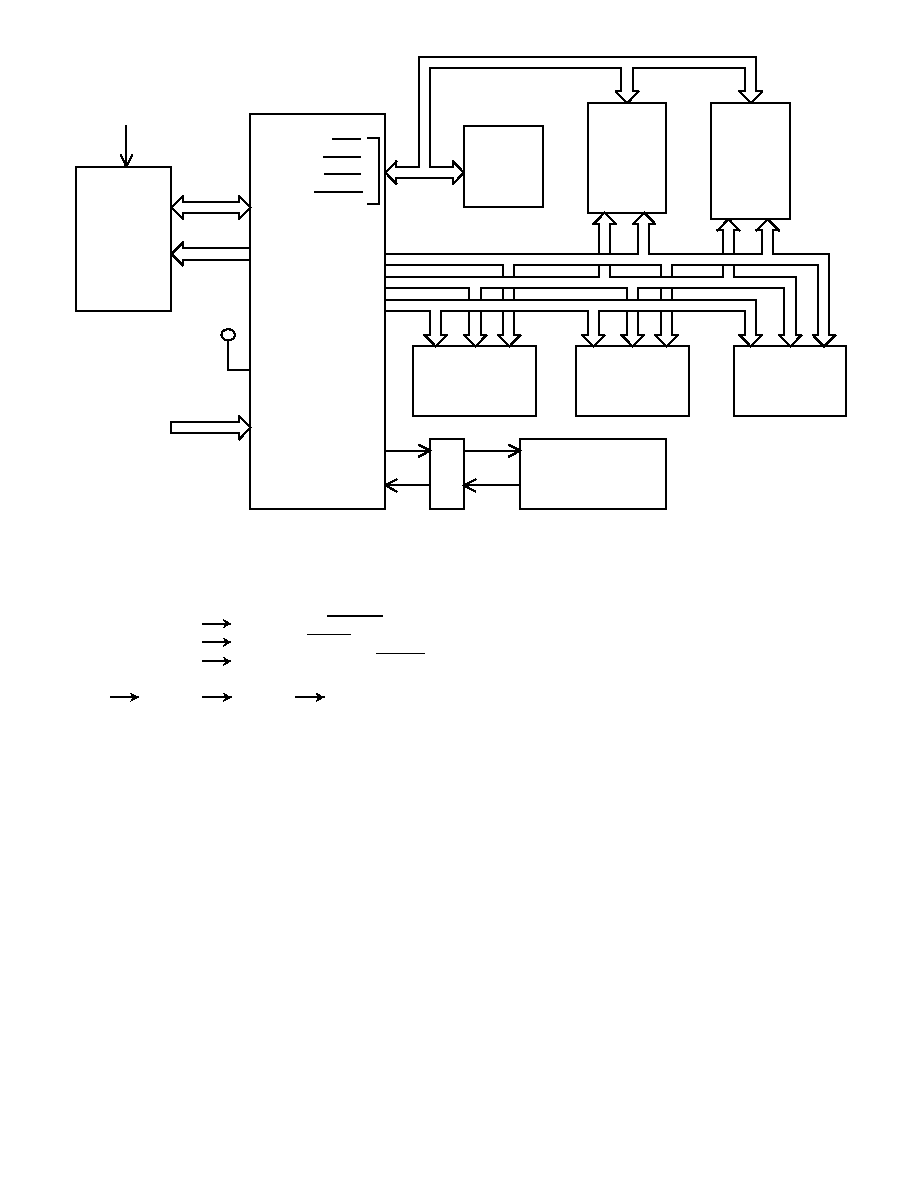

RISC

DATA

RISC

ADD

16

M1750

USER-

DEFINED

SYSTEM

INTERRUPTS

8

UART

I/F

X

C

V

R

1750

PROGRAM/DATA

MEMORY

I/O

DEVICE #1

I/O

DEVICE #2

BUS

ARBITER

DMA

DEVICE

#1

1553

I/F

DMA

DEVICE

#2

OP ADD

OP DATA

CONTROL

BRQ

BGNT

BUSY

BGACK

16

6

Figure 5. The UT1750AR in the MIL-STD-1750 Mode of Operation

4

UT1750AR

CONTAINS RISC MACROS TO

1750

MIL-STD-1750

EMULATE THE MIL-STD-1750A

ISA

EMULATION

ROM

(8K X 16)

+5V

PROGRAMMER’S

CONSOLE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962R0722402VYC | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP256 |

| 5962R8958702VXA | 5 V FIXED POSITIVE LDO REGULATOR, 1 V DROPOUT, CDSO16 |

| 5962R9215311VTA | 32K X 8 STANDARD SRAM, 55 ns, CDFP36 |

| 5962R9215311VTX | 32K X 8 STANDARD SRAM, 55 ns, CDFP36 |

| 5962G9215309VMX | 32K X 8 STANDARD SRAM, 55 ns, CDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962R0253801VZA | 制造商:Analog Devices 功能描述:- Rail/Tube |

| 5962R0720802VXC | 制造商:Texas Instruments 功能描述:ADS5463 RHA QMLV DEVICE |

| 5962R0722601VZA | 制造商:Texas Instruments 功能描述:D/A CONVERTER, 12-BIT - Trays |

| 5962R0722701VZA | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 8-Ch 50 kSPS-1 MSPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| 5962R0722902VXA | 功能描述:低壓差穩(wěn)壓器 - LDO 3-Terminal Adj Reg RoHS:否 制造商:Texas Instruments 最大輸入電壓:36 V 輸出電壓:1.4 V to 20.5 V 回動(dòng)電壓(最大值):307 mV 輸出電流:1 A 負(fù)載調(diào)節(jié):0.3 % 輸出端數(shù)量: 輸出類型:Fixed 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-20 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。