- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373787 > ZL50418GKC (Zarlink Semiconductor Inc.) Managed 16-Port 10/100 M + 2-Port 1 G Ethernet Switch PDF資料下載

參數(shù)資料

| 型號(hào): | ZL50418GKC |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | Managed 16-Port 10/100 M + 2-Port 1 G Ethernet Switch |

| 中文描述: | 管理16端口10/100平方米端口1個(gè)G以太網(wǎng)交換機(jī) |

| 文件頁(yè)數(shù): | 116/163頁(yè) |

| 文件大小: | 2122K |

| 代理商: | ZL50418GKC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)當(dāng)前第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)

ZL50418

Data Sheet

116

Zarlink Semiconductor Inc.

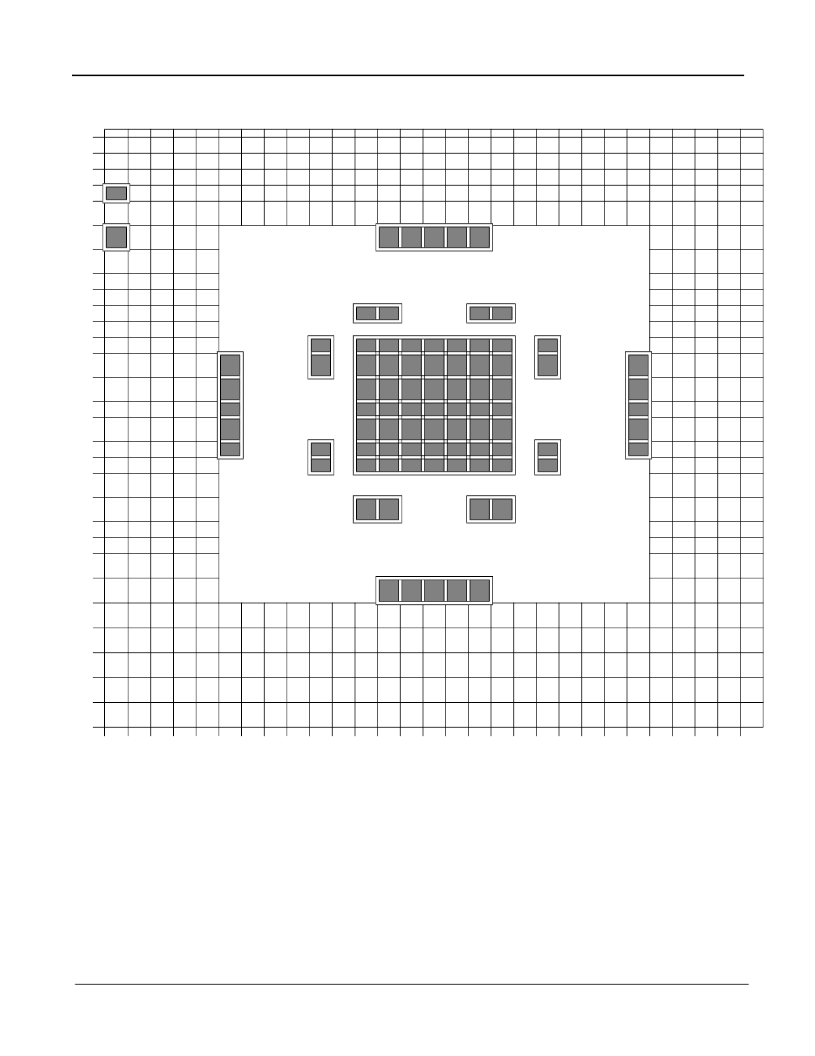

15.1.2 Encapsulated view in managed mode

1

2

3

LA_D

4

LA_D

3

LA_D

2

LA_D

19

LA_D

18

4

LA_D

7

LA_D

6

LA_D

5

LA_D

21

LA_D

20

5

LA_D

10

LA_D

9

LA_D

8

LA_D

23

LA_D

22

6

LA_D

13

LA_D

12

LA_D

11

LA_D

25

LA_D

24

7

LA_D

15

LA_D

14

LA_A

3

LA_D

27

LA_D

26

8

LA_A

4

LA_A

DSC_

LA_O

E_

LA_D

29

LA_D

28

9

LA_O

E0_

LA_O

E1_

LA_W

E_

LA_D

31

LA_D

30

10

LA_A

8

LA_A

7

T_MO

DE1

LA_A

6

LA_A

5

11

LA_A

13

LA_A

12

LA_A

11

LA_A

10

LA_A

9

12

LA_A

16

LA_A

15

LA_A

14

LA_W

E0_

LA_W

E1_

13

LA_A

19

LA_A

18

LA_A

17

LA_D

49

LA_D

48

14

LA_D

33

LA_D

32

LA_A

20

LA_D

51

LA_D

50

15

LA_D

36

LA_D

35

LA_D

34

LA_D

53

LA_D

52

16

LA_D

39

LA_D

38

LA_D

37

LA_D

55

LA_D

54

17

LA_D

42

LA_D

41

LA_D

40

LA_D

57

LA_D

56

18

LA_D

45

LA_D

44

LA_D

43

LA_D

59

LA_D

58

19

P_DA

TA13

P_DA

TA14

P_DA

TA15

LA_D

61

LA_D

60

20

P_DA

TA10

P_DA

TA11

P_DA

TA12

LA_D

63

P_DA

TA8

21

P_DA

TA7

LA_D

62

P_DA

TA9

LA_D

47

LA_D

46

22

P_DA

TA4

P_DA

TA5

P_A2TA3

SCAN

COL

23

P_DA

TA1

P_DA

24

P_A0 P_A1 P_WEUT7

P_DA

TA6

P_DA

TA0

TSTO

UT14

UT13

TSTO

UT15

CRS

M26_

TXCL

K

RESE

RVED

RESE

RVED

RESE

RVED

M26_

TXD9

M26_

TXD4

M26_

TXD7

VCCTXD2

25

26

27

28

29

A

B

LA_D

1

LA_D

0

P_INTP_RDUT8

P_CSUT11

TSTO

TSTO

UT12

M26_

M26_

TXER

TSTO

UT9

TSTO

UT10

SCAN

MOD

E

M26_

MTXC

LK

RESE

RVED

RESE

RVED

M26_

RXD9

M26_

RXD6

M26_

RXD3

M26_

RXD0

TSTO

UT3

TSTO

UT4

TSTO

UT5

TSTO

UT6

C

DAGNDLA_D

SCLK16

LA_C

SCAN

CLK

SCAN

LINK

TSTO

UT0

TSTO

UT1

TSTO

UT2

M26_

RXCL

K

M26_

COL

RESE

RVED

RESE

RVED

M26_

RXD8

M26_

RXD5

M26_

RXD2

GREF

_CLK

1

GREF

_CLK

0

17

E

F

AVCCN_

RESE

TOUT

_

LB_D

45

LB_D

42

LB_D

39

LB_D

36

LB_D

33

LB_A

19

SCAN

EN

LB_D

63

LB_D

62

VCC VCC VCC VCC VCC

M26_

TXEN

M26_

RXDV

G

LB_C

LK

LB_D

46

LB_D

43

LB_D

40

LB_D

37

LB_D

34

LB_A

18

LB_D

47

LB_D

44

LB_D

41

LB_D

38

LB_D

35

LB_D

32

LB_A

20

LB_D

61

LB_D

59

LB_D

57

LB_D

55

LB_D

53

LB_D

51

LB_D

49

LB_D

60

LB_D

58

LB_D

56

LB_D

54

LB_D

52

LB_D

50

LB_D

48

RESE

RVED

RESE

RVED

RESE

RVED

M26_

TXD8

M26_

TXD6

M26_

TXD5

M26_

TXD3

M26_

RXER

RESE

RVED

RESE

RVED

M26_

RXD7

M26_

RXD4

M26_

RXD1

H

J

K

L

VDD VDD

VDD VDD

M

VDD

VSS VSS VSS VSS VSS VSS VSS

VDD

N

VCC

VDD

VSS VSS VSS VSS VSS VSS VSS

VDD

P

LB_A

15

LB_A

10

LB_A

5

LB_O

E0_

LB_A

DSC_

LB_D

15

LB_A

16

LB_A

11

LB_A

6

LB_O

E1_

LB_O

E_

LB_A

3

LB_A

17

LB_A

12

LB_A

7

T_MO

DE0

LB_W

E_

LB_A

4

LB_W

E0_

LB_A

13

LB_A

8

LB_D

31

LB_D

29

LB_D

27

LB_W

E1_

LB_A

14

LB_A

9

LB_D

30

LB_D

28

LB_D

26

VCC

VSS VSS VSS VSS VSS VSS VSS

VCCTXD0

M26_

TXD1

M25_

TXER

M25_

TXEN

RESE

RVED

RESE

RVED

RESE

RVED

M25_

TXD9

MDIO

R

VCC

VSS VSS VSS VSS VSS VSS VSS

VCCCRS

M25_

TXCL

K

MDCK

M25_

RXCL

K

M25_

COL

RESE

RVED

RESE

RVED

T

VCC

VSS VSS VSS VSS VSS VSS VSS

VCC

M25_

MTXC

LK

RESE

RVED

RESE

RVED

M25_

M25_

RXDV

M25_

RXER

RESE

RVED

U

VCC

VDD

VSS VSS VSS VSS VSS VSS VSS

VDD

VCCRVED

RESE

RVED

RESE

RVED

V

VDD

VSS VSS VSS VSS VSS VSS VSS

VDD

W

RVED

Y

LB_D

14

LB_D

11

LB_D

8

LB_D

5

LB_D

13

LB_D

10

LB_D

7

LB_D

4

LB_D

12

LB_D

9

LB_D

6

LB_D

3

LB_D

25

LB_D

23

LB_D

21

LB_D

19

LB_D

24

LB_D

22

LB_D

20

LB_D

18

VDD VDD

VDD VDD

M25_

RXD6

M25_

TXD6

M25_

TXD4

M25_

TXD2

M25_

RXD7

M25_

RXD4

M25_

RXD1

RESE

RVED

M25_

RXD8

M25_

RXD5

M25_

RXD2

RESE

RVED

AA

M25_

TXD7

M25_

TXD5

M25_

TXD3

M25_

RXD3

M25_

RXD0

RESE

RVED

AB

AC

AD

LB_D

2

LB_D

1

LB_D

0

LB_D

17

LB_D

16

VCC VCC VCC VCC VCC

M25_

TXD0

M25_

TXD1

RESE

RVED

RESE

RVED

RESE

RVED

AE

M0_T

XEN

M0_T

XD0

M0_T

XD1

M3_T

XD1

M3_T

XEN

M3_R

XD0

M5_T

XD1

M5_T

XEN

M5_R

XD0

M8_T

XD1

M8_T

XEN

M8_R

XD0

M10_

TXD1

M10_

TXEN

M10_

RXD0

M13_

TXD1

RESE

RVED

M15_

TXD1

RESE

RVED

M15_

TXEN

M15_

RXD0

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

AF

M0_R

XD1

M0_R

XD0

M0_C

RS

M3_T

XD0

M3_C

RS

M3_R

XD1

M5_T

XD0

M5_C

RS

M5_R

XD1

M8_T

XD0

M8_C

RS

M8_R

XD1

M10_

TXD0

M10_

CRS

M10_

RXD1

M13_

TXD0

M13_

CRS

M13_

RXD1

M14_

CRS

RESE

RVED

M15_

RXD1

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

AG

M1_T

XEN

M1_T

XD0

M1_T

XD1

M2_T

XD1

M2_C

RS

M4_T

XD1

M4_C

RS

M6_T

XD1

M6_C

RS

M7_T

XD1

M7_C

RS

M9_T

XD1

M9_C

RS

M11_

TXD1

M11_

CRS

M12_

TXD1

M12_

CRS

M14_

TXD1

M15_

TXD0

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

AH

M1_R

XD0

M1_C

RS

M2_T

XD0

M2_R

XD0

M4_T

XD0

M4_R

XD0

M6_T

XD0

M6_R

XD0

M7_T

XD0

M7_R

XD0

M9_T

XD0

M9_R

XD0

M11_

TXD0

M11_

RXD0

M12_

TXD0

M12_

RXD0

M14_

TXD0

M14_

RXD0

M13_

RXD0

M15_

CRS

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

RESE

RVED

AJ

M1_R

XD1

3

M2_T

XEN

4

M2_R

XD1

5

M4_T

XEN

6

M4_R

XD1

7

M6_T

XEN

8

M6_R

XD1

9

M7_T

XEN

10

M7_R

XD1

11

M9_T

XEN

12

M9_R

XD1

13

M11_

TXEN

14

M11_

RXD1

15

M12_

TXEN

16

M12_

RXD1

17

M14_

TXEN

18

M14_

RXD1

19

RESE

RVED

20

M13_

TXEN

21

RESE

RVED

22

RESE

RVED

23

RESE

RVED

24

RESE

RVED

25

RESE

RVED

26

RESE

RVED

27

1

2

28

29

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL60101 | 12 x 2.7 Gbps Parallel Fiber Optic Link Transmitter and Receiver |

| ZL60101MJD | 12 x 2.7 Gbps Parallel Fiber Optic Link Transmitter and Receiver |

| ZL60102 | 12 x 2.7 Gbps Parallel Fiber Optic Link Transmitter and Receiver |

| ZL60102MJD | 12 x 2.7 Gbps Parallel Fiber Optic Link Transmitter and Receiver |

| ZL60212 | 880 nm High-Performance Single-chip DUPLEX |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL51B | 制造商:YEASHIN 制造商全稱:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL56B | 制造商:YEASHIN 制造商全稱:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL5V1B | 制造商:YEASHIN 制造商全稱:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL5V6B | 制造商:YEASHIN 制造商全稱:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL60001 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:High speed 2.5 Gbps 850 nm VCSEL |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。