- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373783 > ZL30109QDG1 (ZARLINK SEMICONDUCTOR INC) DS1/E1 System Synchronizer with PDF資料下載

參數(shù)資料

| 型號: | ZL30109QDG1 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | DS1/E1 System Synchronizer with |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, 1 MM HEIGHT, LEAD FREE, MS-026ACD, TQFP-64 |

| 文件頁數(shù): | 11/37頁 |

| 文件大小: | 751K |

| 代理商: | ZL30109QDG1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

ZL30109

Data Sheet

11

Zarlink Semiconductor Inc.

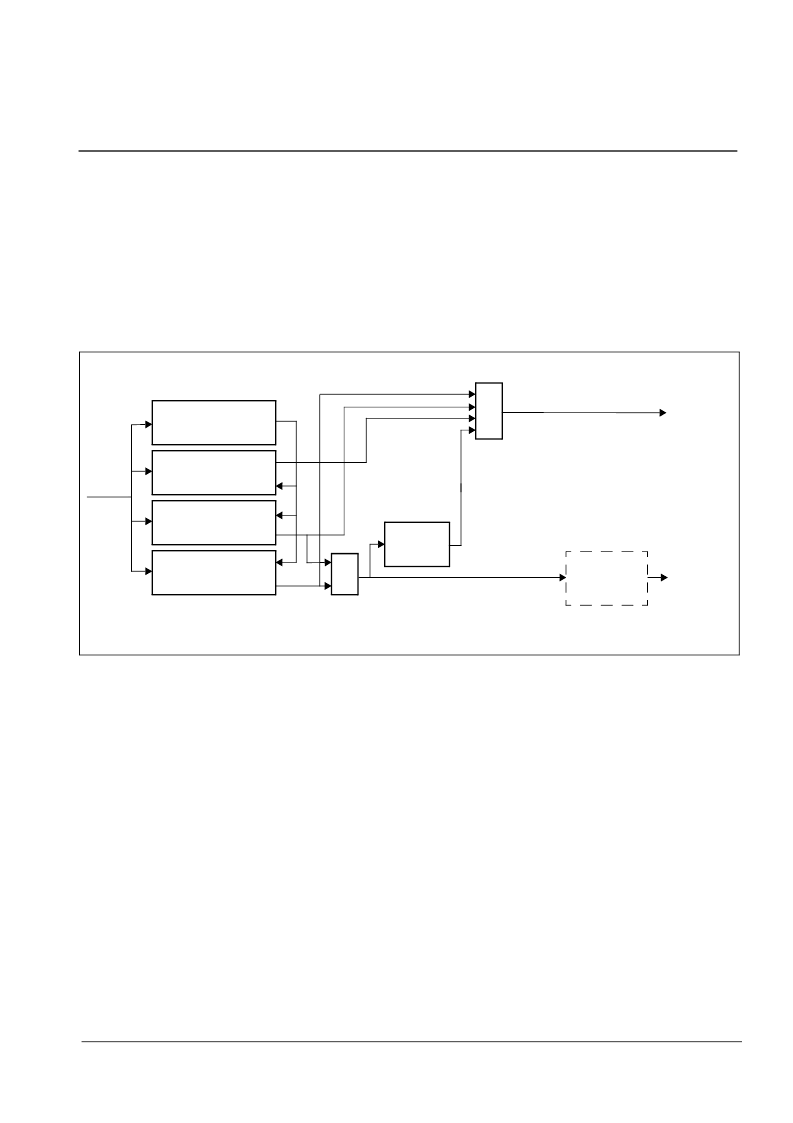

Reference Frequency Detector

: This detector determines whether the frequency of the reference clock is

2 kHz, 8 kHz, 1.544 MHz, 2.048 MHz, 8.192 MHz, 16.384 MHz or 19.44 MHz and provides this information

to the various monitor circuits and the phase detector circuit of the DPLL.

Precise Frequency Monitor

: This circuit determines whether the frequency of the reference clock is within

the applicable out-of-range limits selected by the OOR_SEL pin, see Figure 5, Figure 6 and Table 1. It will

take the precise frequency monitor up to 10 s to qualify or disqualify the input reference.

Coarse Frequency Monitor (CFM)

: This circuit monitors the reference frequency over intervals of

approximately 30

μ

s to quickly detect large frequency changes.

Single Cycle Monitor (SCM)

: This detector checks the period of a single clock cycle to detect large phase

hits or the complete loss of the clock.

Figure 3 - Reference Monitor Circuit

Exceeding the thresholds of any of the monitors forces the corresponding REF_FAIL pin to go high. The single

cycle and coarse frequency failure flags force the DPLL into Holdover mode and feed a timer that disqualifies the

reference input signal when the failures are present for more than 2.5 s. The single cycle and coarse frequency

failures must be absent for 10 s to let the timer re-qualify the input reference signal as valid. Multiple failures of less

than 2.5 s each have an accumulative effect and will disqualify the reference eventually. This is illustrated in Figure

4.

Reference Frequency

Detector

Single Cycle

Monitor

Precise Frequency

Monitor

Coarse Frequency

Monitor

dis/requalify

timer

REF0 /

REF1

OR

OR

REF_DIS= reference disrupted.

This is an internal signal.

Mode select

state machine

HOLDOVER

REF_DIS

REF_FAIL0 /

REF_FAIL1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL30109 | DS1/E1 System Synchronizer with 19.44 MHz Output |

| ZL30109QDG | DS1/E1 System Synchronizer with 19.44 MHz Output |

| ZL30110 | Telecom Rate Conversion DPLL |

| ZL30110LDE | Telecom Rate Conversion DPLL |

| ZL30110LDE1 | Telecom Rate Conversion DPLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30110 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Telecom Rate Conversion DPLL |

| ZL30110LDE | 制造商:Microsemi Corporation 功能描述: 制造商:Microsemi Corporation 功能描述:PLL FREQ SYNTHESIZER TRIPLE 32QFN - Rail/Tube |

| ZL30110LDE1 | 制造商:Microsemi Corporation 功能描述: |

| ZL30110LDF1 | 制造商:Microsemi Corporation 功能描述:PB FREE TELECOM RATE CONVERSION DPLL - Tape and Reel 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE TELECOM RATE CONVERSION DPLL - Tape and Reel |

| ZL30110LDG1 | 制造商:Microsemi Corporation 功能描述:PB FREE TELECOM RATE CONVERSION DPLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC DPLL RATE CONVERSION 32QFN 制造商:Microsemi Corporation 功能描述:IC DPLL RATE CONVERSION 32QFN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。