- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373783 > ZL30109QDG1 (ZARLINK SEMICONDUCTOR INC) DS1/E1 System Synchronizer with PDF資料下載

參數(shù)資料

| 型號: | ZL30109QDG1 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | DS1/E1 System Synchronizer with |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, 1 MM HEIGHT, LEAD FREE, MS-026ACD, TQFP-64 |

| 文件頁數(shù): | 10/37頁 |

| 文件大?。?/td> | 751K |

| 代理商: | ZL30109QDG1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

ZL30109

Data Sheet

10

Zarlink Semiconductor Inc.

3.0 Functional Description

The ZL30109 is a DS1/E1 System Synchronizer providing timing (clock) and synchronization (frame) signals to

interface circuits for DS1 and E1 Primary Rate Digital Transmission links and OC-3/STM-1 links, as well as a

19.44 MHz output for SDH line card applications. Figure 1 is a functional block diagram which is described in the

following sections.

3.1 Reference Select Multiplexer (MUX)

The ZL30109 accepts two simultaneous reference input signals and operates on their rising edges. One of them,

the primary reference (REF0) or the secondary reference (REF1) signal can be selected as input to the TIE

corrector circuit based on the reference selection (REF_SEL) input.

3.2 Reference Monitor

The input references are monitored by two independent reference monitor blocks, one for each reference. The

block diagram of a single reference monitor is shown in Figure 3. For each reference clock, the frequency is

detected and the clock is continuously monitored for three independent criteria that indicate abnormal behavior of

the reference signal, for example; long term drift from its nominal frequency or excessive jitter. To ensure proper

operation of the reference monitor circuit, the minimum input pulse width restriction of 15 nsec must be

observed.

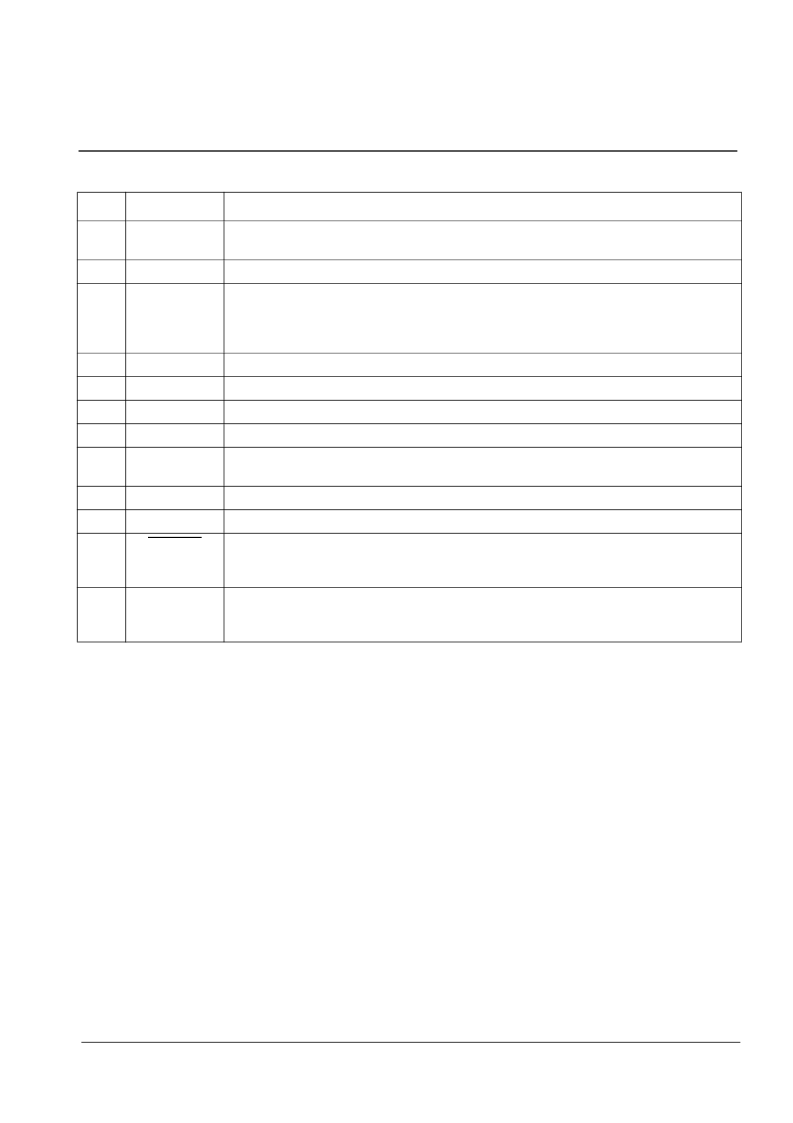

53

REF_SEL

Reference Select (Input)

. This input selects the input reference that is used for

synchronization, see Table 5 on page 20. This pin is internally pulled down to GND.

54

NC

No internal bonding Connection.

Leave unconnected.

55

REF0

Reference (Input).

This is one of two (REF0, REF1) input reference sources used for

synchronization. One of seven possible frequencies may be used: 2 kHz, 8 kHz,

1.544 MHz, 2.048 MHz, 8.192 MHz, 16.384 MHz, or 19.44 MHz. This pin is internally

pulled down to GND.

56

NC

No internal bonding Connection.

Leave unconnected.

57

REF1

Reference (Input).

See REF0 pin description.

58

NC

No internal bonding Connection.

Leave unconnected.

59

IC

Internal Connection.

Connect this pin to ground.

60

OOR_SEL

Out Of Range Selection (Input).

This pin selects the out of range reference rejection

limits, see Table 1 on page 17.

61

V

DD

NC

Positive Supply Voltage.

+3.3 V

DC

nominal.

No internal bonding Connection.

Leave unconnected.

62

63

TIE_CLR

TIE Corrector Circuit Reset (Input).

A logic low at this input resets the Time Interval

Error (TIE) correction circuit resulting in a realignment of the input phase with the output

phase.

64

BW_SEL

Filter Bandwidth Selection (Input).

This pin selects the bandwidth of the DPLL loop

filter, see Table 2 on page 18. Set continuously high to track jitter on the input reference

closely or set temporarily high to allow the ZL30109 to quickly lock to the input reference.

Pin Description (continued)

Pin #

Name

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL30109 | DS1/E1 System Synchronizer with 19.44 MHz Output |

| ZL30109QDG | DS1/E1 System Synchronizer with 19.44 MHz Output |

| ZL30110 | Telecom Rate Conversion DPLL |

| ZL30110LDE | Telecom Rate Conversion DPLL |

| ZL30110LDE1 | Telecom Rate Conversion DPLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30110 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Telecom Rate Conversion DPLL |

| ZL30110LDE | 制造商:Microsemi Corporation 功能描述: 制造商:Microsemi Corporation 功能描述:PLL FREQ SYNTHESIZER TRIPLE 32QFN - Rail/Tube |

| ZL30110LDE1 | 制造商:Microsemi Corporation 功能描述: |

| ZL30110LDF1 | 制造商:Microsemi Corporation 功能描述:PB FREE TELECOM RATE CONVERSION DPLL - Tape and Reel 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE TELECOM RATE CONVERSION DPLL - Tape and Reel |

| ZL30110LDG1 | 制造商:Microsemi Corporation 功能描述:PB FREE TELECOM RATE CONVERSION DPLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC DPLL RATE CONVERSION 32QFN 制造商:Microsemi Corporation 功能描述:IC DPLL RATE CONVERSION 32QFN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。