- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373783 > ZL30109 (Zarlink Semiconductor Inc.) DS1/E1 System Synchronizer with 19.44 MHz Output PDF資料下載

參數(shù)資料

| 型號: | ZL30109 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | DS1/E1 System Synchronizer with 19.44 MHz Output |

| 中文描述: | 的DS1/E1系統(tǒng)同步與19.44 MHz輸出 |

| 文件頁數(shù): | 7/36頁 |

| 文件大小: | 474K |

| 代理商: | ZL30109 |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

ZL30109

Data Sheet

7

Zarlink Semiconductor Inc.

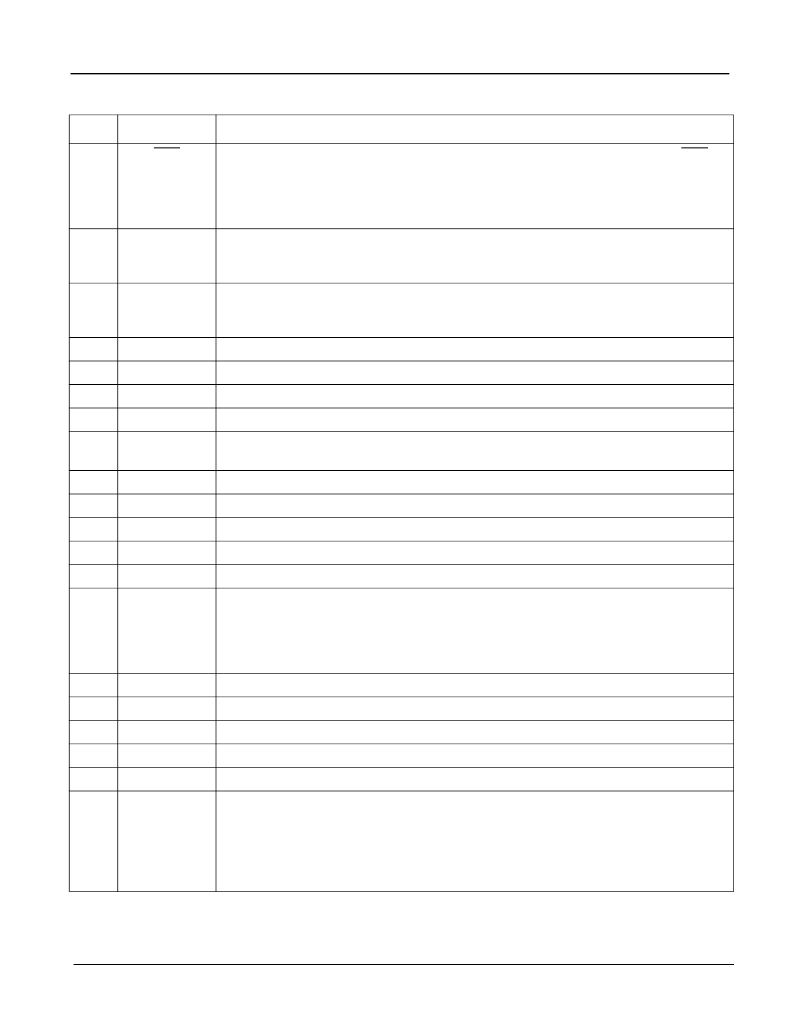

19

RST

Reset (Input).

A logic low at this input resets the device. On power up, the RST pin

must be held low for a minimum of 300 ns after the power supply pins have reached

the minimum supply voltage. When the RST pin goes high, the device will transition

into a Reset state for 3 ms. In the Reset state all outputs will be forced into high

impedance.

20

OSCo

Oscillator Master Clock (Output).

For crystal operation, a 20 MHz crystal is connected

from this pin to OSCi. This output is not suitable for driving other devices. For clock

oscillator operation, this pin must be left unconnected.

21

OSCi

Oscillator Master Clock (Input).

For crystal operation, a 20 MHz crystal is connected

from this pin to OSCo. For clock oscillator operation, this pin must be connected to a

clock source.

22

IC

Internal Connection.

Leave unconnected.

23

GND

Ground.

0 V.

24

NC

No internal bonding Connection.

Leave unconnected.

25

V

DD

Positive Supply Voltage.

+3.3 V

DC

nominal.

Output Selection (Input).

This input selects the signals on the combined output clock

and frame pulse pins, see Table 3 on page 17.

26

OUT_SEL

27

IC

Internal Connection.

Connect this pin to ground.

28

IC

Internal Connection.

Connect this pin to ground.

29

AV

DD

NC

Positive Analog Supply Voltage.

+3.3 V

DC

nominal.

No internal bonding Connection.

Leave unconnected.

30

31

NC

No internal bonding Connection.

Leave unconnected.

32

C1.5o

Clock 1.544 MHz (Output).

This output is used in DS1 applications.

This clock output pad includes a Schmitt input which serves as a PLL feedback path;

proper transmission-line termination should be applied to maintain reflections below

Schmitt trigger levels.

33

AGND

Analog Ground.

0 V

34

AGND

Analog Ground.

0 V

35

AV

CORE

AV

DD

AV

DD

F2ko

Positive Analog Supply Voltage.

+1.8 V

DC

nominal.

Positive Analog Supply Voltage.

+3.3 V

DC

nominal.

Positive Analog Supply Voltage.

+3.3 V

DC

nominal.

Multi Frame Pulse (Output).

This is a 2 kHz 51 ns active high framing pulse, which

marks the beginning of a multi frame.

36

37

38

This clock output pad includes a Schmitt input which serves as a PLL feedback path;

proper transmission-line termination should be applied to maintain reflections below

Schmitt trigger levels.

Pin Description (continued)

Pin #

Name

Description

相關PDF資料 |

PDF描述 |

|---|---|

| ZL30109QDG | DS1/E1 System Synchronizer with 19.44 MHz Output |

| ZL30110 | Telecom Rate Conversion DPLL |

| ZL30110LDE | Telecom Rate Conversion DPLL |

| ZL30110LDE1 | Telecom Rate Conversion DPLL |

| ZL30111 | POTS Line Card PLL |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30109_05 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:DS1/E1 System Synchronizer with |

| ZL30109QDG | 制造商:Microsemi Corporation 功能描述: |

| ZL30109QDG1 | 制造商:Microsemi Corporation 功能描述:DS1/E1 System Synchronizer 64-Pin TQFP 制造商:Microsemi Corporation 功能描述:DS1/E1 SYS. SYNCH WITH 19.44MHZ 制造商:Microsemi Corporation 功能描述:DS1/E1 SYS SYNCHRONIZER 64TQFP - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SYNCHRONIZER DPLL 64TQFP 制造商:Microsemi Corporation 功能描述:IC SYNCHRONIZER DPLL 64TQFP |

| ZL30110 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Telecom Rate Conversion DPLL |

| ZL30110LDE | 制造商:Microsemi Corporation 功能描述: 制造商:Microsemi Corporation 功能描述:PLL FREQ SYNTHESIZER TRIPLE 32QFN - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。