- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373783 > ZL30105QDG1 (ZARLINK SEMICONDUCTOR INC) T1/E1/SDH Stratum 3 Redundant System Clock Synchronizer for AdvancedTC TM and H.110 PDF資料下載

參數(shù)資料

| 型號: | ZL30105QDG1 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | T1/E1/SDH Stratum 3 Redundant System Clock Synchronizer for AdvancedTC TM and H.110 |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, 1 MM HEIGHT, LEAD FREE, MS-026ACD, TQFP-64 |

| 文件頁數(shù): | 28/52頁 |

| 文件大?。?/td> | 1097K |

| 代理商: | ZL30105QDG1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ZL30105

Data Sheet

28

Zarlink Semiconductor Inc.

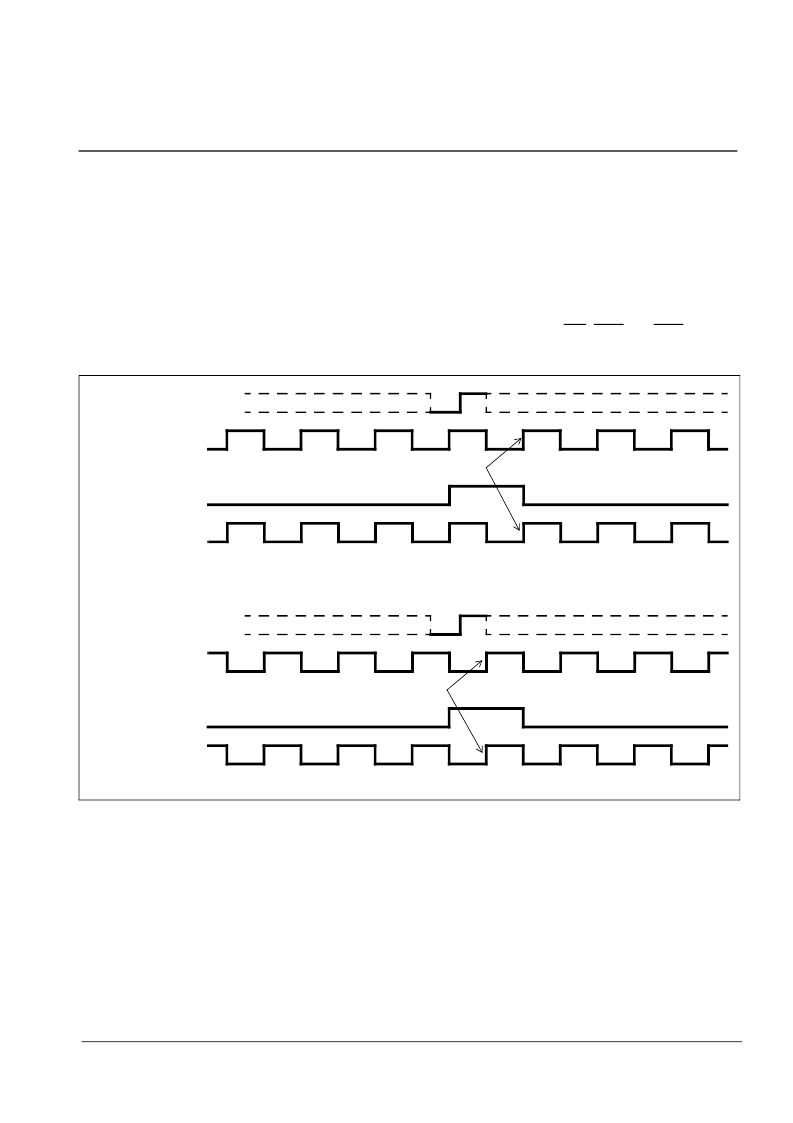

The method of synchronization using REF2 and REF2_SYNC is enabled as soon as a valid 2 kHz or 8 kHz frame

pulse is detected on the REF2_SYNC input. The REF2_SYNC pulse must be generated from the clock that is

present on the REF2 input. The ZL30105 checks the number of REF2 cycles in the REF2_SYNC period. If this is

not the nominal number of cycles, the REF2_SYNC pulse is considered invalid. For example, if REF2 is a

8.192 MHz clock and REF2_SYNC is a 8 kHz frame pulse, then there must be exactly 1024 REF2 cycles in a

REF2_SYNC period. If a valid REF2_SYNC pulse is detected, the ZL30105 will align the rising edges of the REF2

clock and the corresponding output clock such that the rising edge of the F8o/F32o output frame pulse is aligned

with the frame boundary indicated by the REF2_SYNC signal. The rising edges of the REF2 and the corresponding

output clock that are aligned, are the ones that lag the rising edges of the REF2_SYNC and the F8o pulses

respectively. This is illustrated in Figure 18. Many combinations of the ZL30105 clock and frame pulse outputs can

be used as REF2 and REF2_SYNC inputs. In general, the active low frame pulses F4o, F16o and F65o would be

inverted first before used as a REF2_SYNC input.

Figure 18 - Examples of REF2 & REF2_SYNC to Output Alignment

REF2 = C8o

REF2_SYNC = 8 kHz

F8o

aligned

REF2 = C19o

F2ko

C19o

C8o

aligned

REF2_SYNC = 2 kHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL30105 | Power Clamp On Multimeter; DMM Type:Clamp; No. of Digits/Alpha:3-3/4; DMM Response Type:True RMS; Approval Categories:CAT III 600V; Calibrated:No; Current Measuring Range:0-400.0A; Current Setting AC:400A RoHS Compliant: NA |

| ZL30105QDG | Digital Clamp-On Meter; DMM Type:Clamp; No. of Digits/Alpha:3-3/4; DMM Response Type:True RMS; Calibrated:No; Current Setting AC:1000A; Resistance Measuring Range:400 Ohm to 10 MOhm; Voltage Measuring Range AC:600V RoHS Compliant: NA |

| ZL30106QDG1 | SONET/SDH/PDH Network Interface DPLL |

| ZL30106 | SONET/SDH/PDH Network Interface DPLL |

| ZL30106QDG | SONET/SDH/PDH Network Interface DPLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30106 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH/PDH Network Interface DPLL |

| ZL30106_05 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:SONET/SDH/PDH Network Interface DPLL |

| ZL30106QDG | 制造商:Zarlink Semiconductor Inc 功能描述:SONET/SDH/PDH NETWORK INTRFC 64TQFP - Trays 制造商:Microsemi 功能描述:Microsemi ZL30106QDG Communication Misc |

| ZL30106QDG1 | 制造商:Zarlink Semiconductor Inc 功能描述:SONET/SDH/PDH NETWORK INTRFC 64TQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE SONET/SDH/PDH NTWK INTERFACEDPLL |

| ZL30107 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:GbE Line Card Synchronizer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。