參數(shù)資料

| 型號: | XCV812E-6FG900C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 108/118頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 1.8V C-TEMP 900-FBGA |

| 產品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標準包裝: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB數(shù): | 4704 |

| 邏輯元件/單元數(shù): | 21168 |

| RAM 位總計: | 1146880 |

| 輸入/輸出數(shù): | 556 |

| 門數(shù): | 254016 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 900-BBGA |

| 供應商設備封裝: | 900-FBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁當前第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

DS025-2 (v3.0) March 21, 2014

Module 2 of 4

5

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

bined to create a 16 x 2-bit or 32 x 1-bit synchronous RAM,

or a 16 x 1-bit dual-port synchronous RAM.

The Virtex-E LUT can also provide a 16-bit shift register that

is ideal for capturing high-speed or burst-mode data. This

mode can also be used to store data in applications such as

Digital Signal Processing.

Storage Elements

The storage elements in the Virtex-E slice can be config-

ured either as edge-triggered D-type flip-flops or as

level-sensitive latches. The D inputs can be driven either by

the function generators within the slice or directly from slice

inputs, bypassing the function generators.

In addition to Clock and Clock Enable signals, each Slice

has synchronous set and reset signals (SR and BY). SR

forces a storage element into the initialization state speci-

fied for it in the configuration. BY forces it into the opposite

state. Alternatively, these signals can be configured to oper-

ate asynchronously. All of the control signals are indepen-

dently invertible, and are shared by the two flip-flops within

the slice.

Additional Logic

The F5 multiplexer in each slice combines the function gen-

erator outputs. This combination provides either a function

generator that can implement any 5-input function, a 4:1

multiplexer, or selected functions of up to nine inputs.

Similarly, the F6 multiplexer combines the outputs of all four

function generators in the CLB by selecting one of the

F5-multiplexer outputs. This permits the implementation of

any 6-input function, an 8:1 multiplexer, or selected func-

tions of up to 19 inputs.

Each CLB has four direct feedthrough paths, two per slice.

These paths provide extra data input lines or additional local

routing that does not consume logic resources.

Arithmetic Logic

Dedicated carry logic provides fast arithmetic carry capabil-

ity for high-speed arithmetic functions. The Virtex-E CLB

supports two separate carry chains, one per Slice. The

height of the carry chains is two bits per CLB.

The arithmetic logic includes an XOR gate that allows a

2-bit full adder to be implemented within a slice. In addition,

a dedicated AND gate improves the efficiency of multiplier

implementation.

The dedicated carry path can also be used to cascade func-

tion generators for implementing wide logic functions.

BUFTs

Each Virtex-E CLB contains two 3-state drivers (BUFTs)

that can drive on-chip busses. See "Dedicated Routing" on

page 7. Each Virtex-E BUFT has an independent 3-state

control pin and an independent input pin.

Block SelectRAM+ Memory

Virtex-E FPGAs incorporate large block SelectRAM memo-

ries. These complement the Distributed SelectRAM memo-

ries that provide shallow RAM structures implemented in

CLBs.

Block SelectRAM memory blocks are organized in columns,

starting at the left (column 0) and right outside edges and

inserted every four CLB columns (see notes for smaller

devices). Each memory block is four CLBs high, and each

memory column extends the full height of the chip, immedi-

ately adjacent (to the right, except for column 0) of the CLB

column locations indicated in Table 3.

Table 4 shows the amount of block SelectRAM memory that

is available in each Virtex-E device.

Each block SelectRAM cell, as illustrated in Figure 6, is a

fully synchronous dual-ported (True Dual Port) 4096-bit

RAM with independent control signals for each port. The

data widths of the two ports can be configured indepen-

dently, providing built-in bus-width conversion.

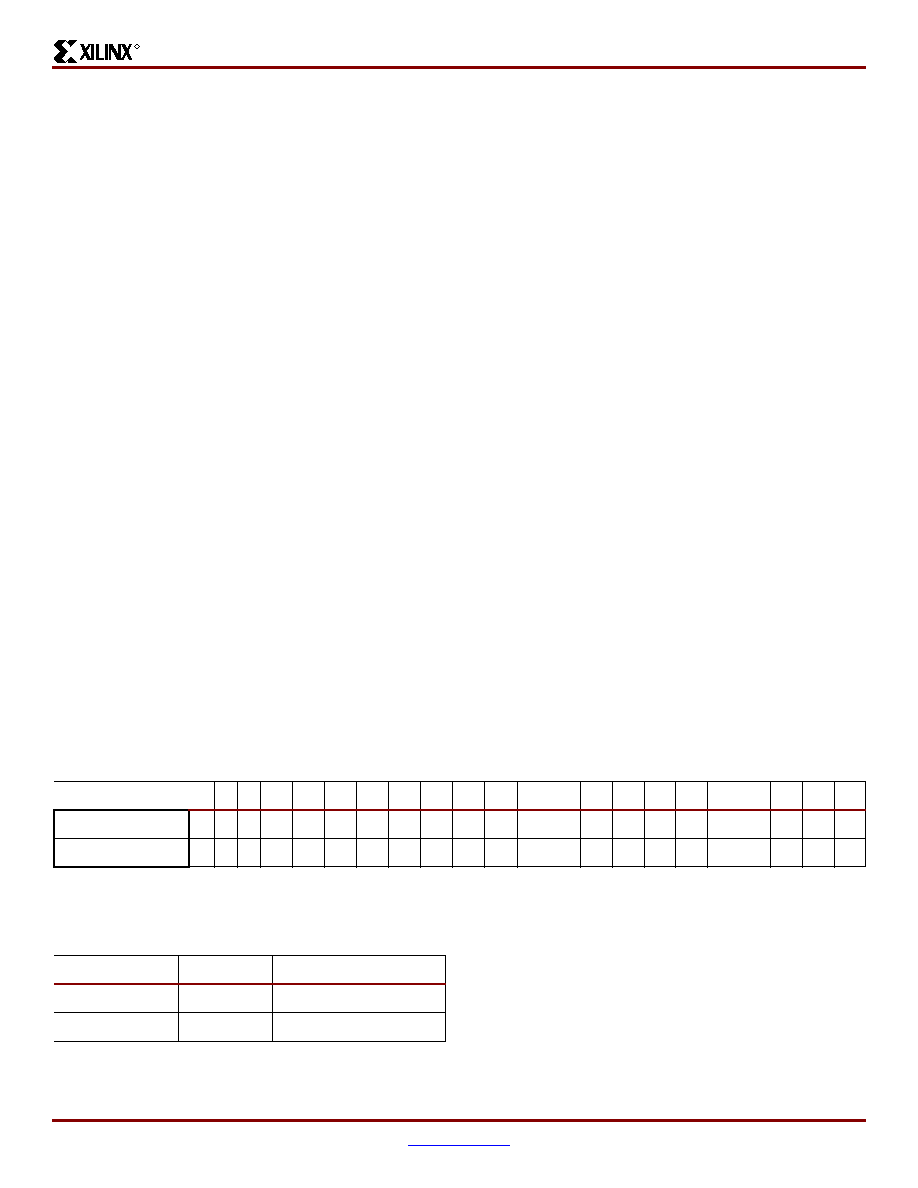

Table 3:

CLB/Block RAM Column Locations

Virtex-E Device

0

4

8

12

16

20

24

28

32

36

40

444852566064

68

72

76

80

84

XCV405E

√ √ √ √

√

√√√√√

XCV812E

√ √ √ √

√

√√√√√√√√√√

Table 4:

Virtex-E Block SelectRAM Amounts

Virtex-E Device

# of Blocks

Block SelectRAM Bits

XCV405E

140

573,440

XCV812E

280

1,146,880

相關PDF資料 |

PDF描述 |

|---|---|

| RCB106DHAR-S621 | EDGECARD 212POS DIP R/A .050 SLD |

| XC6VLX240T-1FFG1759C | IC FPGA VIRTEX 6 241K 1759FFGBGA |

| ACC65DRXN | CONN EDGECARD 130PS .100 DIP SLD |

| RMC65DRYI-S734 | CONN EDGECARD 130PS DIP .100 SLD |

| XC4VSX55-10FF1148I | IC FPGA VIRTEX-4SX 1148FFBGA |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XCV812E-6FG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG404C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG404I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG556C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG556I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復。