- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4214 > XCV405E-7FG676I (Xilinx Inc)IC FPGA 1.8V 676-BGA PDF資料下載

參數(shù)資料

| 型號: | XCV405E-7FG676I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 63/118頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V 676-BGA |

| 產品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標準包裝: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB數(shù): | 2400 |

| 邏輯元件/單元數(shù): | 10800 |

| RAM 位總計: | 573440 |

| 輸入/輸出數(shù): | 404 |

| 門數(shù): | 129600 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 676-BGA |

| 供應商設備封裝: | 676-FBGA(27x27) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁當前第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

DS025-2 (v3.0) March 21, 2014

Module 2 of 4

45

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

LVDS

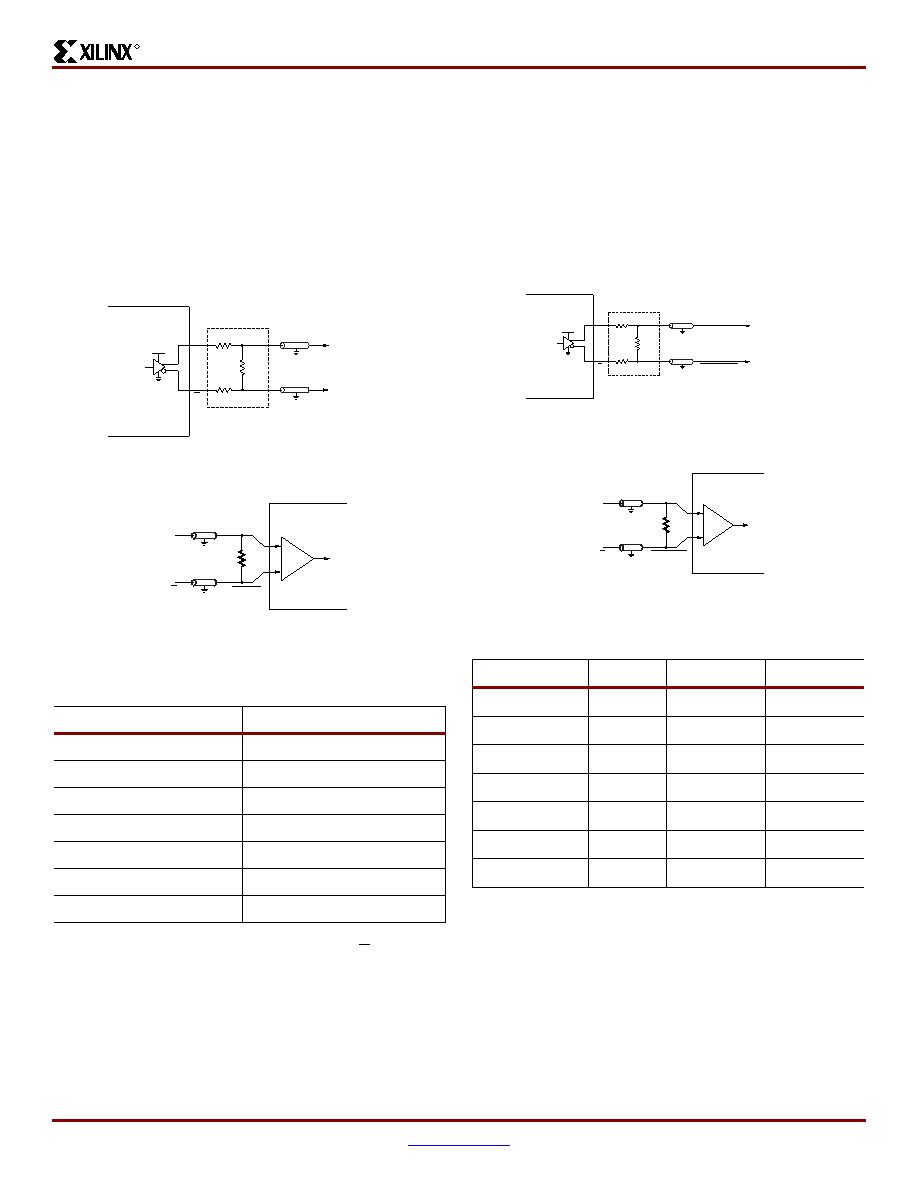

Depending on whether the device is transmitting an LVDS

signal or receiving an LVDS signal, there are two different

circuits used for LVDS termination. A sample circuit illustrat-

ing a valid termination technique for transmitting LVDS sig-

nals appears in Figure 54. A sample circuit illustrating a

valid termination for receiving LVDS signals appears in

information on the specific termination resistor packs shown

can be found on Table 40.

LVPECL

Depending on whether the device is transmitting or receiv-

ing an LVPECL signal, two different circuits are used for

LVPECL termination. A sample circuit illustrating a valid ter-

mination

technique

for

transmitting

LVPECL

signals

appears in Figure 56. A sample circuit illustrating a valid ter-

mination

for

receiving

LVPECL

signals

appears

in

Figure 57. Table 39 lists DC voltage specifications. Further

information on the specific termination resistor packs shown

can be found on Table 40.

Figure 54: Transmitting LVDS Signal Circuit

Figure 55: Receiving LVDS Signal Circuit

Table 38:

LVDS Voltage Specifications

Parameter

Min

Typ

Max

VCCO

2.375

2.5

2.625

VICM(2)

0.2

1.25

2.2

VOCM(1)

1.125

1.25

1.375

VIDIFF (1)

0.1

0.35

-

VODIFF (1)

0.25

0.35

0.45

VOH(1)

1.25

-

VOL(1)

-

1.25

Notes:

1.

Measured with a 100

Ω resistor across Q and Q.

2.

Measured with a differential input voltage =

+/ 350 mV.

x133_19_122799

Q

Z0 = 50Ω

Q

Virtex-E

FPGA

to LVDS Receiver

RDIV

140

R

S

165

R

S

165

2.5V

V

CCO = 2.5V

LVDS

Output

DATA

Transmit

1/4 of Bourns

Part Number

CAT16-LV4F12

x133_29_122799

Q

Z0 = 50Ω

LVDS_IN

Z0 = 50Ω

R

T

100

Ω

Q

DATA

Receive

from

LVDS

Driver

VIRTEX-E

FPGA

+

–

Figure 56: Transmitting LVPECL Signal Circuit

Figure 57: Receiving LVPECL Signal Circuit

Table 39:

LVPECL Voltage Specifications

Parameter

Min

Typ

Max

VCCO

3.0

3.3

3.6

VREF

--

-

VTT

--

-

VIH

1.49

-

2.72

VIL

0.86

-

2.125

VOH

1.8

-

VOL

-

1.57

Note: For more detailed information, see LVPECL DC

x133_20_122799

Q

Z0 = 50Ω LVPECL_OUT

LVPECL_OUT

Z0 = 50Ω

Q

Virtex-E

FPGA

to LVPECL Receiver

RDIV

187

R

S

100

R

S

100

3.3V

DATA

Transmit

1/4 of Bourns

Part Number

CAT16-PC4F12

x133_21_122799

Q

Z0 = 50Ω

LVPECL_IN

Z0 = 50Ω

R

T

100

Ω

Q

DATA

Receive

from

LVPECL

Driver

VIRTEX-E

FPGA

+

–

相關PDF資料 |

PDF描述 |

|---|---|

| XC6VLX195T-1FFG784C | IC FPGA VIRTEX 6 199K 784FFGBGA |

| XC6VCX130T-2FFG784I | IC FPGA VIRTEX 6 128K 784FFGBGA |

| XC4VLX60-11FF668I | IC FPGA VIRTEX-4LX 668FFBGA |

| XC4VLX60-12FFG668C | IC FPGA VIRTEX-4 LX 60K 668FCBGA |

| XC4VLX60-11FFG668I | IC FPGA VIRTEX-4 LX 60K 668FCBGA |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XCV405E-7FG900C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7FG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-8BG404C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-8BG404I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-8BG556C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復。